一種專用高速數據記錄器的設計和實現

在持續數據采集存儲系統中,數據存儲是一項關鍵技術。常規的數據記錄器多采用總線型設計思路。過去的做法是通過內存將采集和存儲聯系起來。外部采集到的數據經由PCI總線送入系統內存,然后再由主機把數據寫入磁介質存儲器。由于數據兩次經由PCI總線進出內存,總線效率降低一半,速度也降低很多。

隨著對PCI總線和SCSI總線接口協議以及計算機系統結構的了解愈加深入,現在多采用映射內存及總線主控技術,使SCSI適配器對PCI采集設備直接進行訪問。由于避開了系統內存這一環節,速度得到了很大的提高。

一種常規的做法是在微機系統加一塊PCI-SCSI接口卡,使數據通過高速PCI接口,由SCSI總線處理器將高速數據寫入SCSI硬盤。其缺點在于數據速度受到PCI帶寬的限制,而且由于對微機系統的依賴,系統難以實現模塊化設計。

本文提出了一種專用的高速數據記錄系統設計。設計脫離了微機系統,由DSP控制將高速數據實時持續的寫入SCSI硬盤,在存儲容量和傳輸速度等方面都具有很大的優勢。此外,設備還支持數據的高速回寫。

1. SCSI總線和硬盤

SCSI是英文Small Computer System Interface的縮寫,譯為小型計算機系統接口。SCSI是美國ANSI9.2委員會定義的計算機和外設之間的接口標準。本系統采用SCSI硬盤,因為SCSI接口本身具有很多優點:(1)SCSI提供了一個高速傳輸通道,目前Ultra320 SCSI總線數據傳輸速度可以達到320MB/s,雖然在實際應用中達不到這個理論值,但百兆比特的數據傳輸速度完全可以達到;(2)由于有專門的SCSI協議控制器和內嵌的處理器處理SCSI信號和數據傳輸,因此SCSI設備對CPU占用率低。此外還支持多任務工作模式;(3)SCSI總線占用系統資源少,還可以同時串接多臺不同設備,最多時可達15個;(4)SCSI硬盤在標識硬盤扇區時使用了線形的概念,即硬盤只有順序的第1扇區、第2扇區,第n扇區,不像IDE硬盤的“柱面/磁頭/扇區”三維格局。這種線形編排方式的優點是訪問時間小,可以有效地加快磁盤存取速度,尤其在持續大容量數據存儲時,優勢更為明顯。此外,通過掛接多個硬盤組成磁盤陣列可以大大地增加數據的存儲容量。

2. 系統結構設計

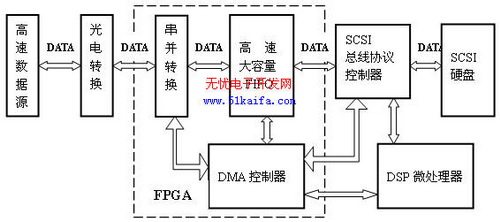

整個系統的設計結構[1]框圖如圖1所示,主要包括以下幾部分:高速數據源(不在本文設計中)、光電轉換和串并轉換單元、高速大容量的數據緩存、微處理器、DMA控制器、SCSI協議處理器以及高速SCSI硬盤。下面逐一介紹。

2.1 光電轉換和串并轉換單元

系統的高速數據源為光接口,記錄器接收到光信號后,首先經過光電轉換變為串行的電信號,再經過串并轉換變為16位的并行數據。

采用光接口的主要原因在于:光纖通道(Fibre Channel) 是一種高性能的串行數據接口,支持SCSI、ATM等上層數據傳輸協議,具有可靠性高、速度快和傳輸距離遠的特點,特別適合高速大容量的信息傳輸。

2.2 高速大容量的數據緩存

圖1:高速數據記錄器結構框圖

數據緩存的主要作用在于實現速度匹配,為高速DMA傳輸做好準備。

普通的SRAM存儲器只有一套數據、地址和控制總線,無法同時進行讀寫操作。雙口RAM有兩套數據、地址和控制總線,可以同時進行讀寫操作。但其編譯碼電路復雜,而且價格相對較高。由于我們對數據不進行任何處理,只是單純的數據存儲,緩存單元在結構上相當于一個先入先出(FIFO: First In First Out),先到的數據先被存儲。設計中,我們利用現場可編程門陣列(FPGA:Field Programmable Gate Array)實現一個高速FIFO,省去了復雜的編譯碼電路,大大簡化了系統設計。而且,從外部數據接口看來,設備就是一個寫不滿的FIFO,也大大簡化了對設備數據接口的操作。

2.3 微處理器

用來控制設備中各部分的工作,實現設備的特定功能。高速數據記錄器主要實現數據持續高速存儲,對數據處理的速度要求較高。通常采用數字信號處理器(DSP:Digital Signal Processing)作為微處理器。

2.4 DMA控制器

設計中,為保證大量數據的高速持續傳輸,采用直接存儲器訪問(DMA:Direct Memory Access)方式,因此需要DMA控制器單元。為了簡化電路,提高效率,設備采用FPGA構造一個單獨的DMA控制器。

2.5 SCSI協議處理器

無論DSP還是FPGA,通常都不會集成SCSI協議控制器。因此我們用專門的SCSI協議控制器來實現SCSI協議,輔助DSP來實現SCSI協議和通信。

2.6 SCSI硬盤

采用SCSI硬盤可以實現數據高速存儲,而且通過增加磁盤數目可以很方便的擴展存儲容量。

3. 硬件電路的實現

前面我們已經逐一介紹了系統各部分的功能,下面我們介紹一下高速數據記錄器的硬件電路的實現。

由于設備采用光接口,當高速數據流進入設備后,首先我們需要進行光電轉換和串并轉換。光電轉換可以通過專門的光電轉換芯片實現,而串并轉換我們利用某些FPGA內嵌的收發器模塊(Transceiver)來實現。這樣做既可以保證數據的高速傳輸,又可以有效地保證時鐘同步,實現字對齊,可靠性高。

高速數據緩存通常采用專用FIFO,但價格較高。我們利用FPGA來實現一個大容量的FIFO,即簡化了系統,又提高了效率。前面已經介紹過專用的DMA控制器連接電路復雜,我們用FPGA來設計一個單獨的DMA控制器同樣可以簡化電路,提高效率。

設計中,串并轉換單元、高速數據緩存和DMA控制器都利用FPGA編程實現(如圖1虛線所示)。用高度集成的FPGA取代分立元件進行高速數據傳輸設計是本文的一個重要特點。

微處理器我們采用德克薩斯儀器(TI:Texas Instruments)公司生產的數字信號處理器MS320F206;SCSI協議控制器則選用Qlogic公司的FAS660。

下面我們對SCSI協議控制器FAS660[3]做進一步的介紹。

FAS660是Qlogic公司推出的一款高性能SCSI引擎,它源于Qlogic公司的TEC485三重嵌入式控制器系列。可提供Fast-160的同步傳輸速率,支持先進的SCSI自動配置模式SCAM的1層和2層協議。內部嵌有微控制器,能夠用編程的方法靈活的協調SCSI作業隊列。FAS660和主流SCSI接口芯片最大的區別在于:主流SCSI接口芯片采用的是PCI總線接口,而FAS660采用的是微處理器和DMA接口的結構。這使得FAS660更為靈活,可以根據需要進行多種接口設計,尤其適合應用在一些專用SCSI總線控制場合。

4. 系統的軟件設計

在硬件設計的基礎上,還需要軟件模塊

負責對相關硬件進行控制和協調,最終實現SCSI協議、硬盤的控制和DMA傳輸等。軟件模塊的設計是本系統的難點和重點。本系統中,軟件設計主要分為兩部分:DSP控制軟件和FPGA實現的DMA控制器,此外還有FPGA實現的串并轉換和高速FIFO。程序的優劣關系到整個系統數據存儲的性能,下面分別進行討論。

4.1 FPGA設計

FPGA設計主要包括異步收發器模塊、高速異步FIFO緩沖模塊、DMA控制器模塊以及時鐘生成模塊。FPGA作為設計中的重要一部分,用來實現數據傳輸的準備(包括串并轉換、高速緩沖以及加入奇偶校驗、CRC校驗)和對讀寫邏輯的控制。

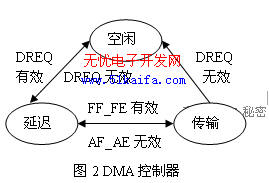

圖2 DMA控制器狀態機

DMA控制器是FPGA設計的主要工作。我們通過DMA控制器,實現傳輸數據的控制邏輯,同時對前端傳來的數據(沒有任何保護)加以保護(通常指奇偶校驗保護和CRC校驗保護)。它的控制邏輯相當簡單。當FAS660發送數據傳輸請求(聲明DREQ),如果FIFO非空,則經過延時后,開始數據傳輸(聲明DACK)。FAS660的讀寫操作非常相似,但也有一些差別。讀操作在DACK有效后的第二個DMA時鐘周期開始傳輸,而寫操作在DACK有效后的第一個DMA時鐘周期開始傳輸。在FPGA設計的內部邏輯時尤其需要注意。

Altera公司為StratixGX系列FPGA提供了gxb(吉比特收發器) 、fifo(先入先出)、pll(鎖相環)等MEGAFUCTION,通過對它們進行例化可以很方便地實現高速收發器,高速FIFO和時鐘生成等模塊。

4.2 DSP控制軟件

基于FAS660的系統可以通過DSP微處理器和FAS660(內部有單獨的微控制器和SCSI控制器用來實現SCSI協議)的協調工作來實現系統功能。一般來說,要完成一次數據交換必須完成SCSI總線的仲裁、選擇、消息、命令、數據和狀態等階段,這些階段通過為處理器TMS320F206對FAS660寄存器[4]的讀寫命令來實現。

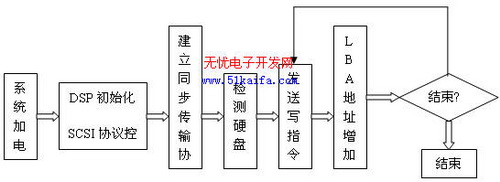

SCSI控制軟件流程如圖3所示。首先初始化設備,然后建立同步傳輸協議,檢測硬盤。硬盤準備好后就可以進行數據傳輸。

圖3 DSP控制軟件流程

5. 結束語

本文介紹了一種光接口的專用高速數據記錄器的設計。它脫離了微機平臺,用DSP微處理器做控制,用專門的SCSI總線控制器處理SCSI總線信號,并建立了一個高速DMA通道,將數據高速持續的存儲到SCSI磁盤陣列中。設計速度高,容量大,可移植性好,可以靈活應用到各種系統中。

本文作者創新點:

1.專用型記錄器的設計思路,避免了總線帶寬限制,可以達到更高的傳輸速度。

2.用DSP做為本地CPU,控制整個系統,脫離了微機系統,實現了模塊化設計。

3.用高度集成的FPGA取代了多個分立元件(FIFO,串并轉換,DMA控制器)。

4.源端數據采用光接口傳輸,可靠性高,速度快。

參考文獻:

[1]姜鳳山,雷宏. 一種基于FAS466的合成孔徑雷達高速數據記錄器的設計.電子技術應用,2004.6。

[2]何蘇勤,王忠勇.TMS320C2000系列DSP原理及實用技術.北京:電子工業出版社,2003.9。

[3]Qlogic Corporation.FAS660 fast architecture SCSI processor technical manual,2002.7。

[4]Qlogic Corporation.FAS660 Fast Architecture SCSI Processor Designer’Guide,2003.1。

[5]吳志祥,汪波,基于ISCSI的存儲系統實現方法. 微計算機信息,2006,3-3。

合成孔徑雷達相關文章:合成孔徑雷達原理

評論