基于FPGA的水聲信號采樣存儲系統設計

摘要:為了提高水聲傳感器網絡通信系統試驗和算法研究的效率,水聲傳感器網絡節點需要具有水聲通信的原始波形數據的記錄功能。本文設計了一種水聲信號采樣存儲系統,實現了數據變速率AD采集、數據環形存儲、數據連續讀取、數據飛讀等功能。該系統具有結構清晰,集成度高,工作可靠等優點,可以有效提高水聲傳感器網絡試驗的效率。

本文引用地址:http://www.j9360.com/article/189977.htm1 引言

近幾十年來,隨著世界各國對海洋開發和利用步伐的加快,對海洋信息進行連續實時監 測的意義越來越重要。水聲無線傳感器網絡(Underwater AcouSTic sensor network,簡稱 UW-ASN)是海洋環境立體監測系統中的研究熱點,它由大量具有計算和通信能力的傳感器 節點組成,各節點被分布在指定的海域,執行連續的協同監測任務。鑒于水聲信道的帶寬有 限、海洋噪聲復雜、具有多途效應和多普勒效應[1],這些特殊性給UW-ASN 中的水聲通信、 協議設計等方面帶來了很大的挑戰,增加了傳感器網絡設計的復雜性。

為了充分了解水聲通信過程中的數據變化,方便對于信道特性分析以及通信方式的選 擇,以及大量傳感器網絡節點之間通信數據的存儲,傳感器節點必須具備數據采集功能。傳 統的水聲數據采集存儲系統主要由數據采集板卡組成,能夠滿足數據采集功能,缺點是體積 大,便攜性差,難以作為傳感器節點的組成部分應用于實際設計中。

本文針對這一問題,提出了基于SOPC(System ON Programmable Chip)的設計方案[2],利 用其配置靈活、擴展性強、接口豐富等優點,以Altera 公司的Cyclone II 系列FPGA 為基 礎,設計傳感器節點數據采集存儲系統,降低了設計的風險,完善了傳感器節點功能要求。

2 采樣存儲系統概述

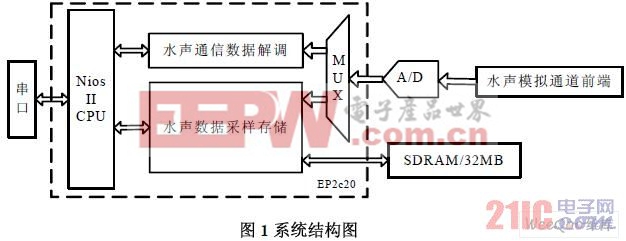

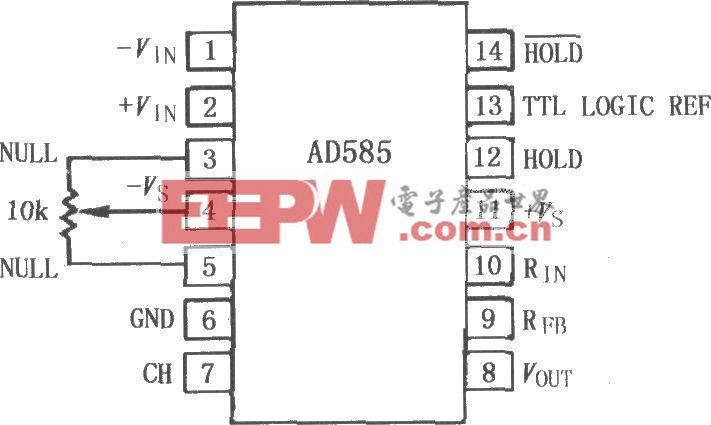

本設計系統的結構如圖1 所示,在整個傳感器節點的系統當中,將AD 芯片輸出的12 位數據,通過設計SDRAM 控制IP 核,實現數據變速率AD 采集、數據環形存儲、數據環 形讀取、以及數據飛讀(實時數據讀取)等功能。同時,對于NiosII CPU 設計串口(UART) 協議,以便前置機與傳感器節點通信,實現不同命令操作功能,方便對水聲試驗過程中波形 數據的變化進行仿真處理,以滿足試驗要求。

本設計采用 MICRO 公司的MT48LC32M8A2 型號容量為32Mbyte 的SDRAM,芯片地 址線為25 位,每個地址存儲16 位數據。根據水聲通信試驗要求,聲波頻率為40KHz,每 個正弦波采樣16 個點,則采樣時鐘要求至少640KHz,本系統設計采樣時鐘最大40MHz。 同時,環形存儲深度最大為32Mbyte,每次采樣存儲數據占2byte,則至少可以采樣25 秒正 弦波數據。環形存儲區域大小,以及采樣時鐘都可以進行參數化配置,能夠滿足試驗要求。 系統整體分為硬件邏輯設計,與軟件程序設計兩部分。

評論