DDR SDRAM在高速數據采集系統中的應用

在數據處理中為了更好地對被測對象進行處理和分析,研究人員們把重點更多的放在高速、高精度、高存儲深度的數據采集系統的研究上

由于A/D芯片及高性能的FPGA的出現,已經可以實現高速高精度的數據處理,則進行大批量高存儲深度的數據處理成為當前要解決的主要問題

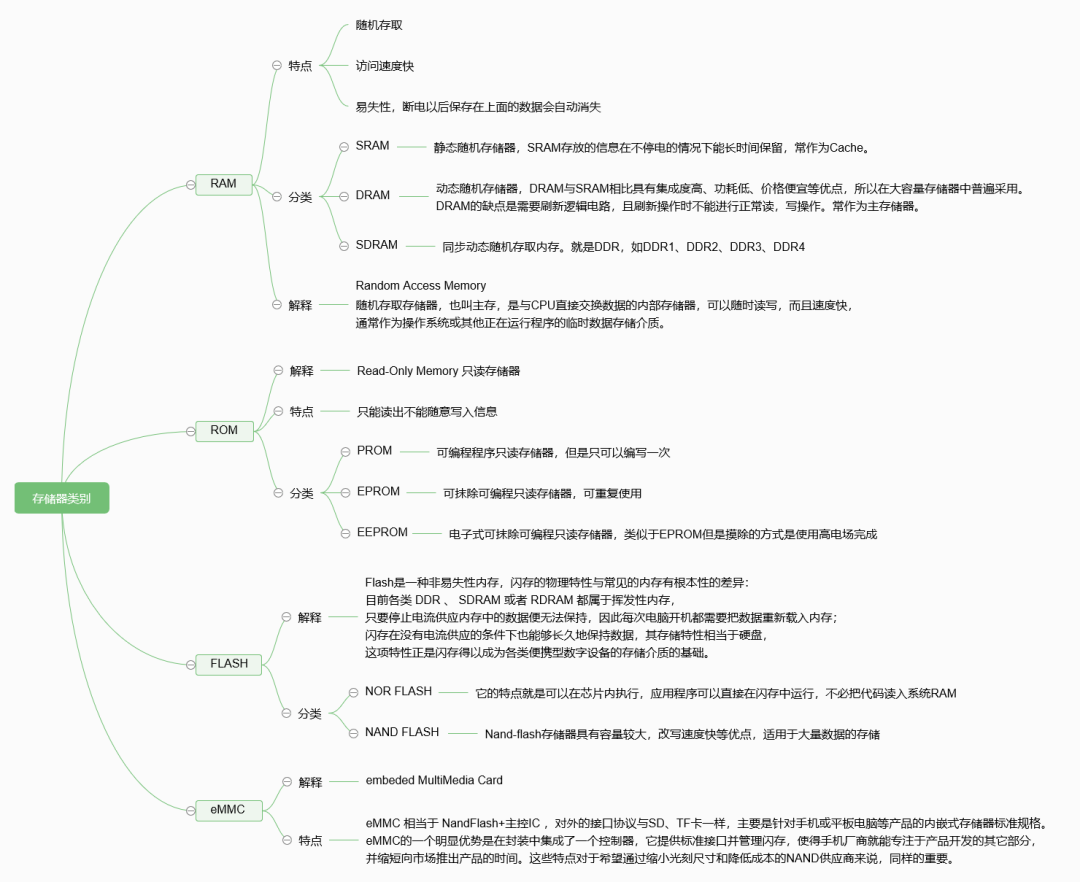

l 常用存儲器的比較

現在用于數據采集系統的存儲器常見的有先進先出存儲器(FIFO)、靜態RAM和SDRAM等 FIFO由于容量和速度的限制,不是實現大容量存儲的首選

FIFO由于容量和速度的限制,不是實現大容量存儲的首選 目前,最為常見的存儲器就是靜態存儲器(SRAM),靜態存儲器有控制簡單、功耗低的優點

目前,最為常見的存儲器就是靜態存儲器(SRAM),靜態存儲器有控制簡單、功耗低的優點 當前大容量的SRAM可以達4 MB,存儲時鐘速率250 MHz

當前大容量的SRAM可以達4 MB,存儲時鐘速率250 MHz

如果要實現單通道32 M的存儲深度和200 M的數據傳輸速度,就要由8×1片SRAM拼合起來才能實現 但由于每片SRAM都要有獨立的地址對應存儲的數據,這對設計者進行制版和布線都是一個極大的挑戰

但由于每片SRAM都要有獨立的地址對應存儲的數據,這對設計者進行制版和布線都是一個極大的挑戰 與靜態存儲器相比,單數據率動態存儲器(SDR SDRAM)具有存儲密度高、速度快等特點,數據線位寬可最大可以達到64 b,很適合于高速采樣系統

與靜態存儲器相比,單數據率動態存儲器(SDR SDRAM)具有存儲密度高、速度快等特點,數據線位寬可最大可以達到64 b,很適合于高速采樣系統 標準的SDR SDRAM可以達到的時鐘頻率達100 MHz以上,如果要滿足系統存儲速率的要求則至少需要有2×12 b的數據位寬,而目前并沒有64 b或32 b的SDRSDRAM,則需要使用多片拼合

標準的SDR SDRAM可以達到的時鐘頻率達100 MHz以上,如果要滿足系統存儲速率的要求則至少需要有2×12 b的數據位寬,而目前并沒有64 b或32 b的SDRSDRAM,則需要使用多片拼合 這樣,對應于一個通道的存儲就至少需要有2片12 b的動態存儲器才能滿足存儲的需要,顯然成本比較高

這樣,對應于一個通道的存儲就至少需要有2片12 b的動態存儲器才能滿足存儲的需要,顯然成本比較高

雙速率同步動態隨機訪問存儲器(DDR),是在SDRAM存儲技術上發展而來的一種新型存儲器件,在計算機行業得到了廣泛的應用 其特點是采用了雙倍速率結構實現高速操作,其在同一時間內傳輸的數據量是SDRSDRAM的2倍,最大傳送數據的時鐘速率可達400 MHz,而存儲一個通道的數據只需要1片16 b的DDR,并且單位存儲成本和SDR SDRAM相比并沒有提高

其特點是采用了雙倍速率結構實現高速操作,其在同一時間內傳輸的數據量是SDRSDRAM的2倍,最大傳送數據的時鐘速率可達400 MHz,而存儲一個通道的數據只需要1片16 b的DDR,并且單位存儲成本和SDR SDRAM相比并沒有提高 因而,對于高速數據采集系統,無論從成本還是性能方面考慮,采用DDR作為系統的存儲器件是合適的

因而,對于高速數據采集系統,無論從成本還是性能方面考慮,采用DDR作為系統的存儲器件是合適的 但DDR卻帶來了相對復雜的控制工作,不僅需要與SDRSDRAM一樣進行定時刷新,而且較SDRAM增加了新的控制信號和使用了新的電平標準

但DDR卻帶來了相對復雜的控制工作,不僅需要與SDRSDRAM一樣進行定時刷新,而且較SDRAM增加了新的控制信號和使用了新的電平標準

2 DDR的基本工作原理

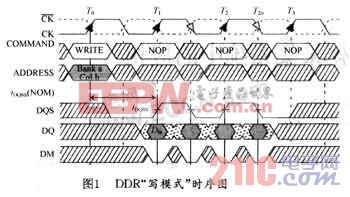

所謂DDR的雙倍速率結構,即在數據隨路時鐘的上升沿和下升沿各發送一次數據,這樣在一個時鐘周期內可完成雙倍速率的數據傳輸 由于DDR的控制邏輯比較復雜,這里只對其寫模式下的工作原理進行介紹,如圖1所示

由于DDR的控制邏輯比較復雜,這里只對其寫模式下的工作原理進行介紹,如圖1所示

|

其中根據DDR的時序要求在寫模式下,寫命令和隨路時鐘的第1個上升沿要有一個固定的時間間隔tDQSS

其中根據DDR的時序要求在寫模式下,寫命令和隨路時鐘的第1個上升沿要有一個固定的時間間隔tDQSS 為了在對DDR進行讀寫時能夠正確地存儲和讀取數據,應該嚴格地按照廠家提供的芯片手冊上的時序要求進行邏輯控制設計

為了在對DDR進行讀寫時能夠正確地存儲和讀取數據,應該嚴格地按照廠家提供的芯片手冊上的時序要求進行邏輯控制設計 下面對DDR的邏輯控制的設計和實現流程進行簡單的介紹

下面對DDR的邏輯控制的設計和實現流程進行簡單的介紹

3 DDR控制模塊的設計

根據DDR芯片控制要求,在設計中將DDR主控制模塊分為5個子模塊,分別是初始化模塊、外部刷新模塊、主狀態機模塊、地址模塊和命令輸出模塊 其具體組成如圖2所示

其具體組成如圖2所示

|

初始化模塊在系統啟動之后馬上對DDR進行配置,使其達到正確的時序和配置要求

初始化模塊在系統啟動之后馬上對DDR進行配置,使其達到正確的時序和配置要求 DDR初始化的流程圖如圖3所示

DDR初始化的流程圖如圖3所示

評論