燦芯半導體推出兩項創新技術用于DDR物理層

一站式定制芯片及IP供應商——燦芯半導體日前宣布推出用于高速DDR物理層中的Zero-Latency (零延遲)和True-Adaptive(真自適應)兩項技術。這兩項技術已經開始在12/14 FinFET, 22/28nm的DDR4/LPDDR4,4x高性能物理層IP上進行部署,將為客戶帶來更高效、更穩定的全新體驗。

本文引用地址:http://www.j9360.com/article/202207/435987.htm

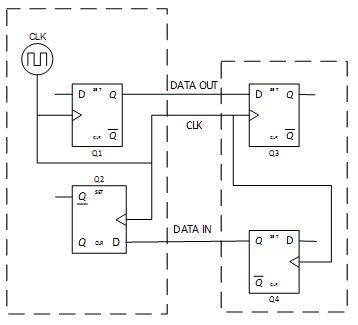

Zero-Latency (零延遲) 技術在讀數據通路上,采用了兩種可選的、獨特的采樣方式進行數據轉換,而不像其他DDR物理層供貨商采用FIFO進行跨時鐘域轉換,此技術將延遲降低到最小,節省了硅面積。

True-Adaptive (真自適應)技術始終對芯片內的電壓溫度、芯片與顆粒之間的往返延遲的變化以及讀數據/讀數據選通信號的延遲偏差進行跟蹤,選擇適當的時機進行補償。采用這個技術后,用戶只需上電后進行一次訓練,之后即讓物理層自行跟蹤補償,可完全避免重新訓練帶來的帶寬損失。

燦芯半導體工程副總裁劉亞東表示:“燦芯半導體深耕DDR物理層技術多年,一直致力于創新架構革新,采用基于這些技術的物理層IP的客戶正不斷增加,未來燦芯半導體也將致力于更好地滿足客戶需求,為客戶帶來更高的價值。”

評論