三維封裝DDR2存儲器VD2D4G72XB191XX3U6測試

摘要:與其它存儲器相比DDR2 SDRAM操作較為復雜,封裝成一個位寬72bit的模塊后,測試難度進一步增加,針對這一問題,本文提出了基于Magnum 2測試系統的DDR2SDRAM存儲模塊VD2D4G72XB191XX3U6的測試方法,對直流參數、交流參數以及功能進行了測試,論述了測試的關鍵技術。

本文引用地址:http://www.j9360.com/article/202205/434701.htmDDR2 SDRAM 以高速、大容量著稱,但是缺點也很明顯,操作復雜、掉電丟失數據、需定時刷新,這給測試帶來了不小的難度。尤其是在航空航天領域,對小型化要求比較高,產生了一種利用三維封裝的技術將多片芯片垂直堆疊制作成一個存儲模塊,這樣在不占用額外PCB 面積的情況下增大了容量。VD2D4G72XB191XX3U6 就是利用該技術制作而成,在增加容量的同時,將數據位寬從16 bit 擴展到72 bit,滿足了用戶的特殊要求。

同時為了應對航空航天對可靠的特別要求,需要對DDR2 SDRAM 進行覆蓋性測試[1],即對芯片內部每個存儲單元進行不同pattern 的讀寫測試,測試驗證的同時還需要兼顧時間效益,經濟效益。本文介紹了基于MagnumII 存儲器測試系統對DDR2 SDRAM 存儲模塊VD2D4G72XB191XX3U6 的直流參數、交流參數和功能覆蓋性測試的方案。

1 MagnumII 存儲器測試系統[2]

Magnum II 存儲器測試系統是Teradyne 公司生產的存儲器專用測試系統,每個Site Assembly Board 具有128 數字通道,每個測試通道均有獨立的時序和電平。Magnum II 測試系統有著強大的算法向量生成器APG(Algorithmic Pattern Generator),最大能夠支持24 bit行選、24 bit 列選、36 bit 數據位寬和18 個片選。

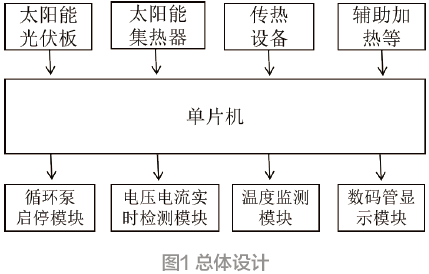

2 VD2D4G72XB191XX3U6存儲器結構

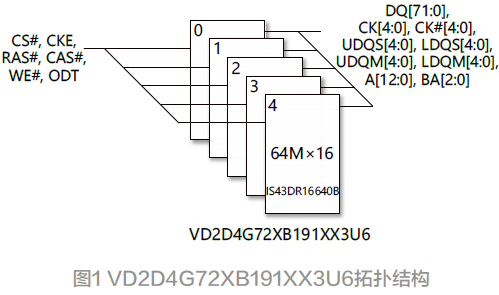

VD2D4G72XB191XX3U6 的拓撲結構如圖1 所示,內部采用5 片ISSI 公司生產的IS43DR16640B 芯片,單顆芯片容量為64 M×16 bits,分3 層進行疊裝,通過灌封、切割、金屬化、激光雕刻等工序生產而成。內部5 個芯片的片選(#CE)、地址總線[A12:0] 合并引出,數據總線DQ[71:0] 并聯引出,將5 片數據寬度為16 bit的芯片擴展成為72 bits 的存儲模塊,其主要特性如下:

● 總容量:4G bit;

● 工作電壓:1.8 V±0.1 V;

● 數據寬度:72 bit;

● 時鐘頻率:333 MHz;

● BL:4,8;

● 刷新周期:64 ms;

● 封裝形式:SOP70。

3 初始化

DDR2 SDRAM 產品在上電使用前需進行初始化,并對模式寄存器(Mode Register)進行配置,確定所需要的突發長度(Burst Length)、突發類型(Burst Type)、CAS 延時等。初始化時需遵循以下步驟[3]:

Step1:上電后保持CKE 和ODT 低電平,VDD 電壓上升時間應小于200 ms;

Step2:保持穩定時鐘;

Step3:電壓穩定不少于200 us 后,CKE 才能置為邏輯高電平,同時發送NOP 或Deselect 命令;

Step4: 等待400ns, 等待時只能發送NOP或Deselect 命令,發送Precharge All 命令;

Step5:配置EMR2;

Step6:配置EMR3;

Step7:配置EMR 使能DLL;

Step8:配置MR,復位DLL;

Step9:發送Precharge All 命令;

Step10:發送兩次以上的Auto-Refresh 命令;

Step11:配置MRS,A8 = 0;

Step12:等待200 個周期,執行OCD 校準;

Step13:DDR2 SDRAM 產品初始化完成。

具體時序見下圖:

圖2 初始化和配置模式寄存器時序

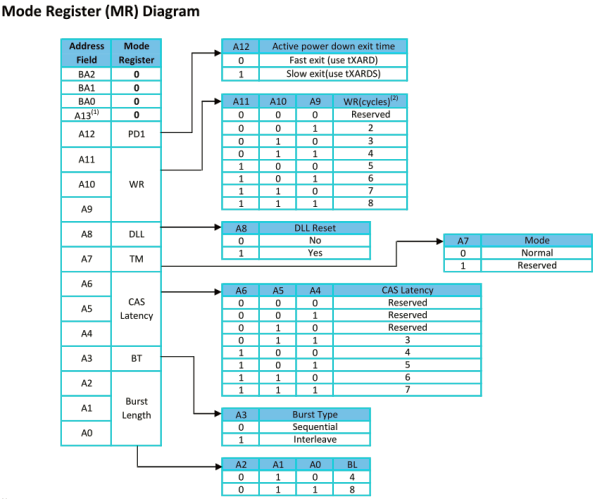

模式寄存器(MR)的配置參數見圖3。

圖3 模式寄存器(MR)配置參數

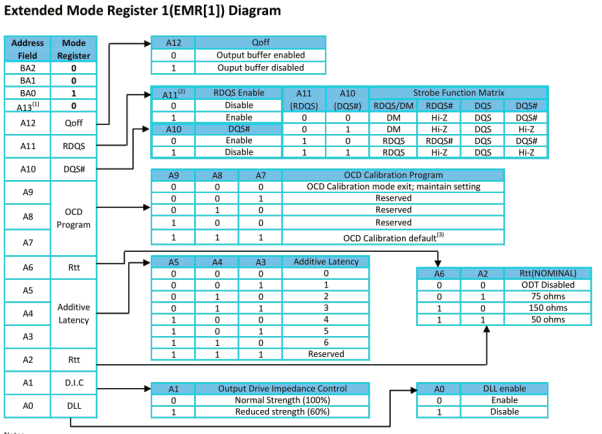

擴展模式寄存器1(EMR1)的配置參數見圖4 。

圖4 擴展模式寄存器1(EMR1)

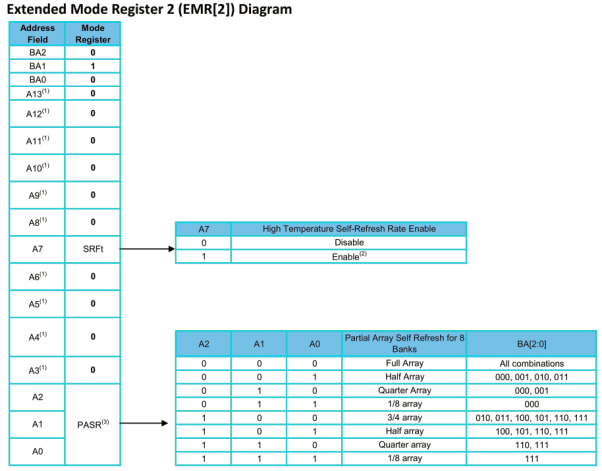

擴展模式寄存器2(EMR2)的配置參數見圖5。

圖5 擴展模式寄存器2(EMR2)

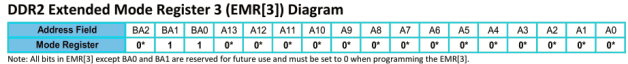

擴展模式寄存器3(EMR3)的配置參數見圖6。

圖6 擴展模式寄存器3(EMR3)

4 直流參數測試

直流參數測試主要包括:開/ 短路測試(O/S);連通性測試(continuity),通過測試每個引腳內部保護二極管的管壓降是否正常來判斷引腳的連通性是否正常,一般來說測試時必須先進行連通性測試;輸入漏電流(ILIH/ILIL)和輸出漏電流(ILOH/ILOL)是在電源電壓為0 時,輸入引腳和輸出引腳施加高電平和低電平的電流,該電流反映的是引腳之間的直流阻抗;IDD 測試的是芯片工作時或休眠時消耗的電流,該電流反映的是芯片的功耗;輸出高/ 低電平測試(VOH/VOL)測試的是DQ 引腳在輸出高電平和輸出低電平時的電壓大小。

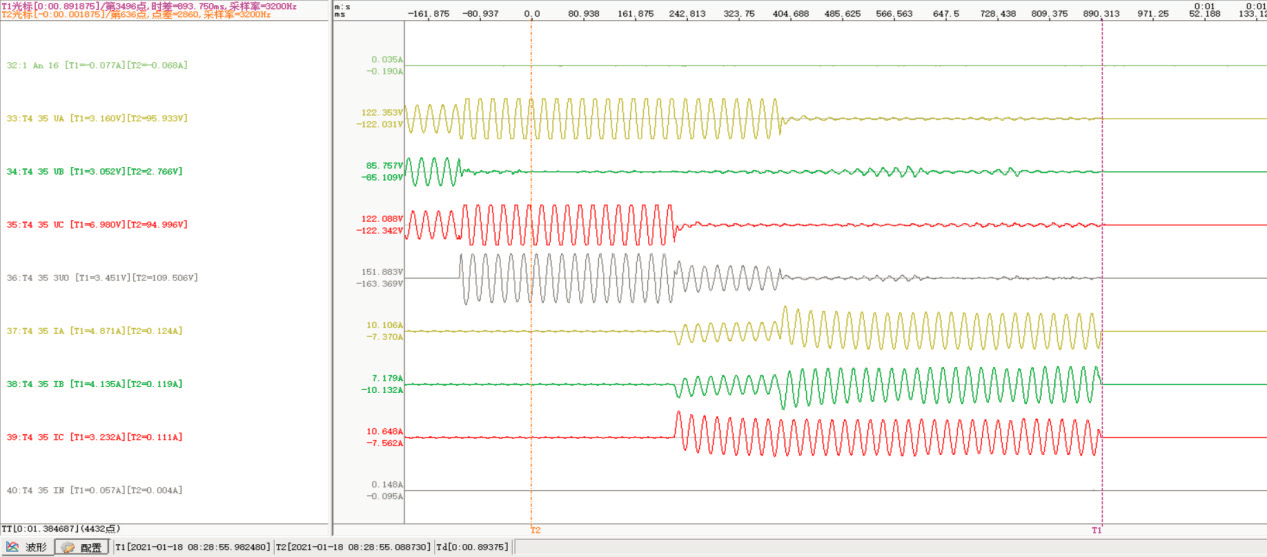

5 交流參數測試

交流參數表征的是芯片的工作性能,一般用搜索法來測試交流參數,下面以在Magnum 2 測試系統上測試tAC參數為例來介紹測試機如何進行交流參數的測試,tAC時鐘上升沿到數據輸出延時(Address to Output Delay),該參數越小則產品響應速度越快。

搜索法的具體思路為假設t0時刻地址有效,隨后在t0+tSTEP進行讀數據,如果讀取成功,則tAC=t0+tSTEP,如果讀取失敗則在t0+2tSTEP時讀取數據,如此循環直到讀取成功為止。搜索法比較簡單,tSTEP的大小決定了測試的精度,如果tSTEP設置的比較小,那么測試耗用的時間勢必較長。

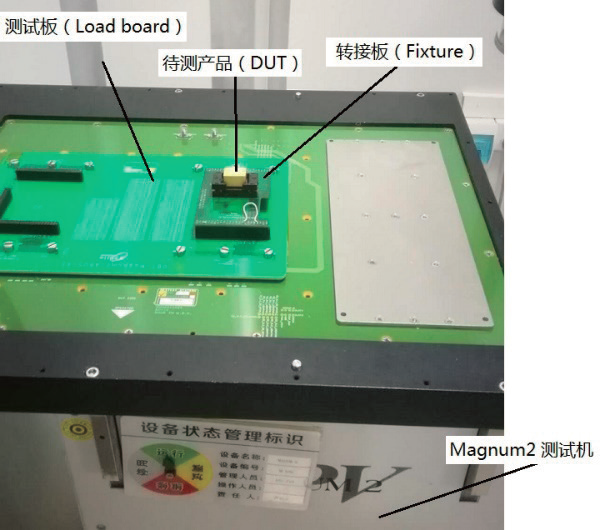

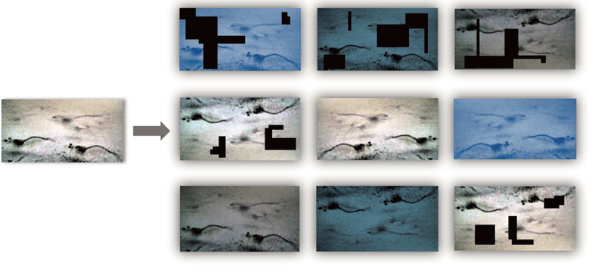

測試前現將芯片裝載到測試夾具上,然后將夾具安裝到測試系統的測試板(Loadboard)上,見圖7。Magnum 2 的測試軟件是在VC 下編寫的,文件pin_assignments.cpp 中定義芯片的各引腳,并定義引腳與Magnum 2 系統測試通道的連接關系,這樣就實現了芯片與測試系統的連接。在文件voltage.cpp 中定義電源電壓、輸入高低電平的電壓值以及DQ 引腳的負載電流,文件timing.cpp 中定義的是各引腳在每個周期(Cycle)中的波形,文件pin_scramble.cpp 中定義的是各引腳與向量生成器(APG)的連接關系,以上就完成了交流測試前的配置工作。

圖7 Magnum 2測試系統

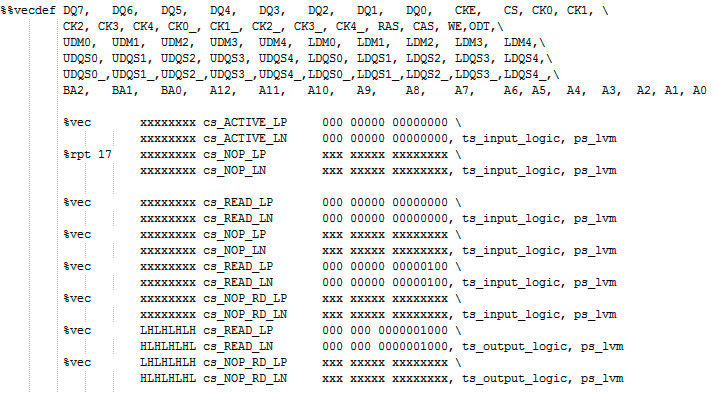

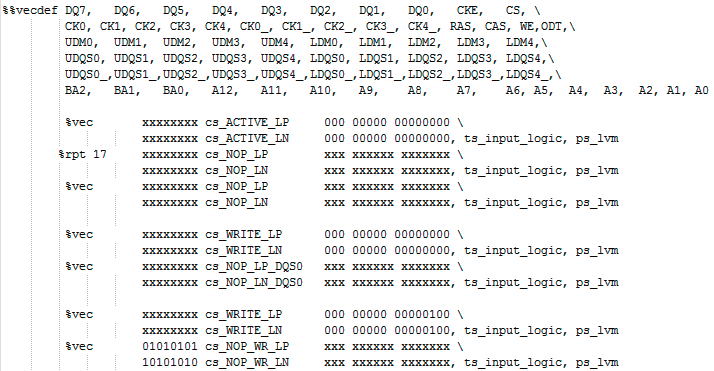

芯片的功能是邏輯向量(logic pattern)來實現的,在VC6.0 下向量代碼如下圖所示。

圖8 讀向量代碼

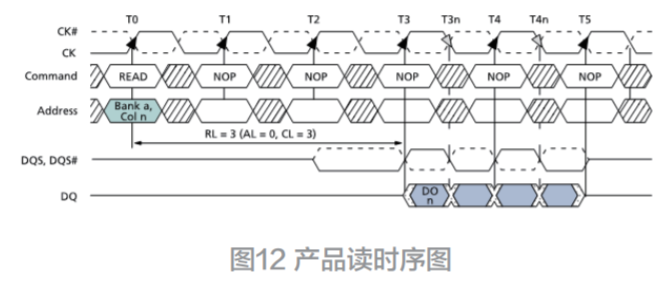

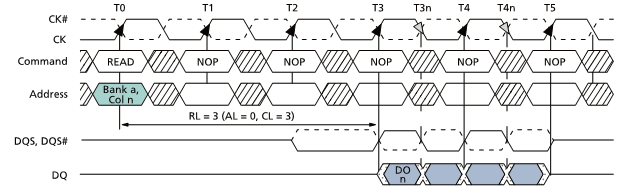

不同于EEPROM、SRAM、MRAM 器件,DDR2SDRAM 器件在進行讀寫操作前需先對目標行(Row)進行激活(Active)。激活完成后發送讀命令和地址,等待CAS 延遲后才能讀取數據,讀時序圖見圖12。

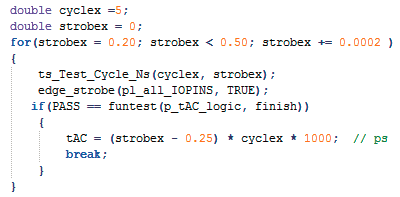

圖9 為搜索法的測試代碼,該代碼中設置測試周期為200 ns,搜索步長為1 ps,搜索范圍為1 ns~2.5 ns,如果測試通過則停止搜索。搜索法簡單方便,是一種常用的交流參數測試方法,如果精度要求不高,則步長可以適當加長以提高測試效率。

圖9 搜索法代碼

6 功能測試

存儲器的功能算法有多種,如全0、全1、棋盤格、反棋盤格、累加數、march 等等,不同的算法檢測的故障不同,測試的覆蓋性不同,耗用的時間也不同,可以根據測試的目的來選擇。

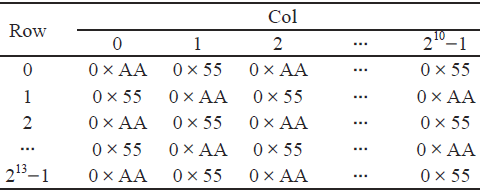

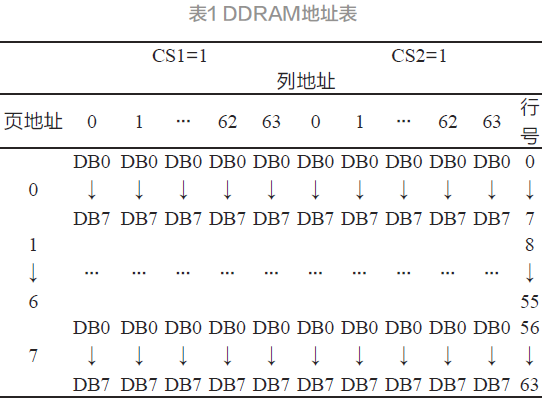

以棋盤格算法為例對產品進行功能測試,表1 為棋盤格算法向量表。由表1 可知,每個存儲單元存儲的數據與周圍存儲單元存儲的數據互為反碼,因此在讀寫時,每個周期(cycle)DQ 管腳的電平都改變一次。

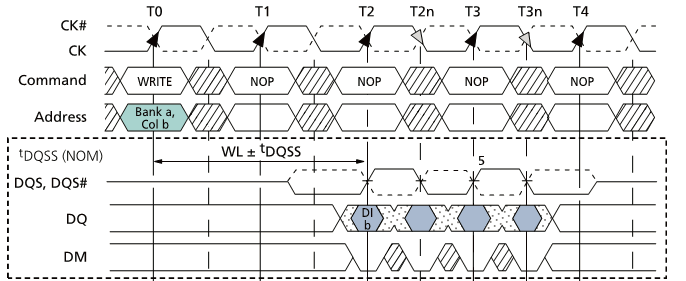

存儲在進行操作時,應該嚴格按照時序圖來進行。圖10 為產品的寫時序圖,命令、地址和數據均在時鐘上升沿被鎖存。

表1 棋盤格向量

圖10 寫時序圖

寫操作的向量代碼如圖11 所示,與圖8 中的讀操作類似,在進行寫操作前,需要先對目標行進行激活操作,并等待tRCD 時間后才能進行寫操作。

圖11 寫向量代碼

圖12為產品的讀時序圖,讀向量代碼見圖8 。

圖12 產品讀時序圖

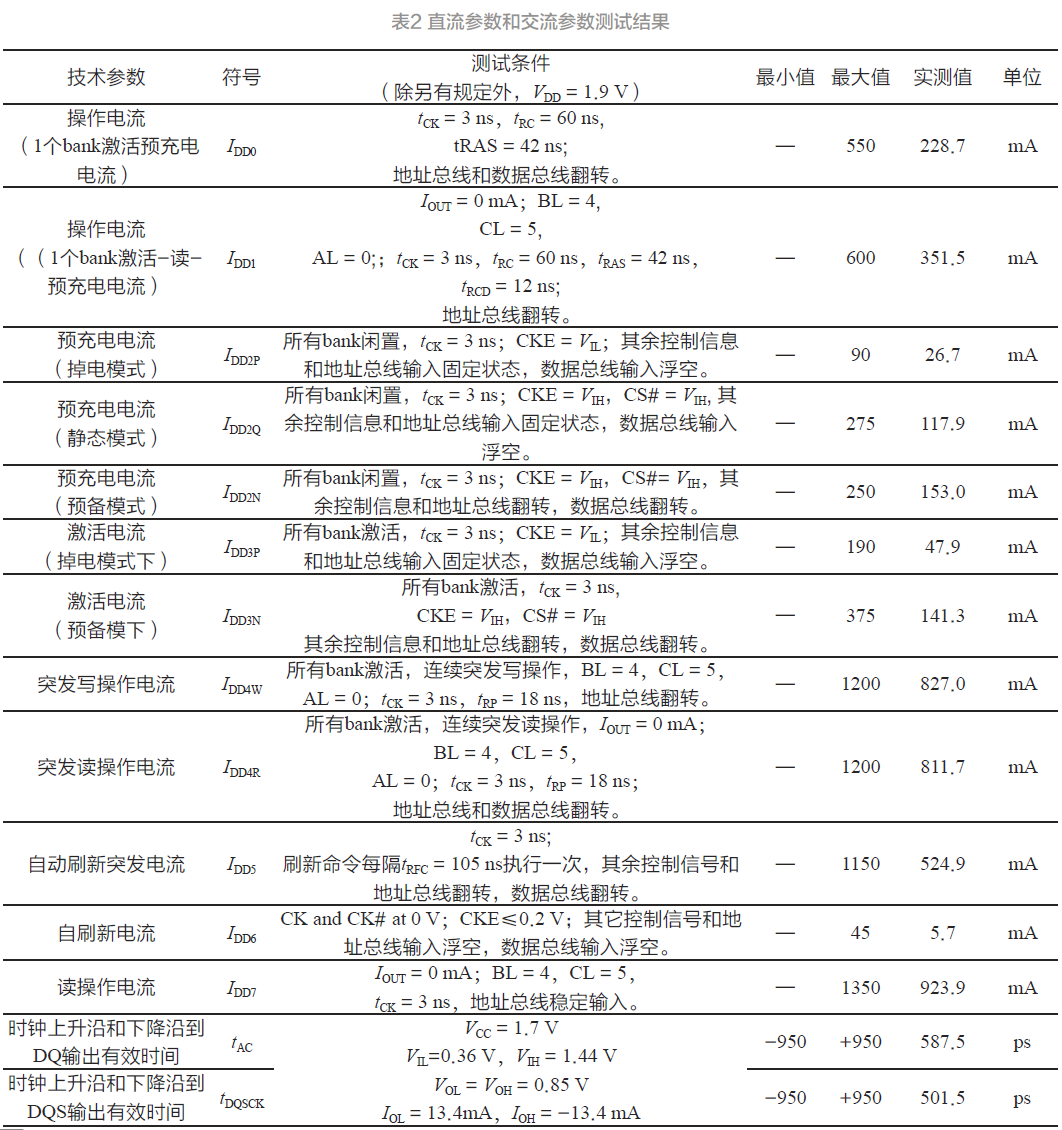

7 測試結果

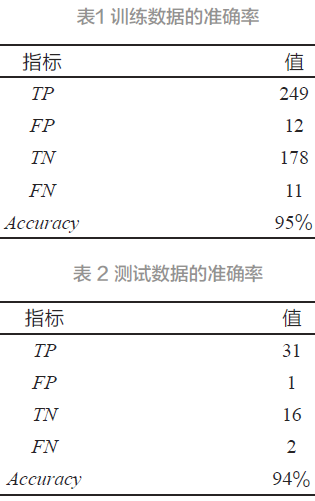

表2 所示為產品的參數標準以及實測結果,由表2的測試結果可知,在規定的測試條件下實測結果均在標準范圍內,證明了測試方法的正確性。

8 結論

本文介紹了Magnum 2 測試系統和產品存儲器,提出了一種測試產品存儲器的測試方法以及測試代碼的編寫,并對該存儲器的連通性、直流參數、交流參數和功能進行了實測,驗證了測試正確性。

參考文獻:

[1] 鄭小牧.SDRAM存儲器測試的實現與優化[D].北京:中國科學院大學,2013.

[2] NEXTEST.Magnum 2 Test System PV Maintenance Manual[R].

[3] ISSI Datasheet for 1Gb DDR2 SDRAM IS43DR16640B,Rev.G[S].

(本文來源于《電子產品世界》雜志2022年5月期)

評論