如何實現FPGA到DDR3 SDRAM存儲器的連接

延時鎖定環路(DLL)在整個PVT范圍內將相位保持在一個固定位置。DLL模塊的相位比較器用于將兩個輸入之間的相位差保持在零。實現的方法是均勻地修正DLL模塊中的特定延時(10-16)。用于更新DLL中某個延時模塊的控制信號還被發送到DQS輸入路徑中的時延模塊。例如,可以利用DLL中的全部16個延時單元和DQS相移輸入路徑中的第4個延時抽頭來實現90°的相移:

或者選擇DLL中的10個延時單元和DQS相移輸入路徑中的抽頭4來實現36°的相移:

或120°:

該DLL采用頻率基準為每個DQS引腳中的延時鏈動態產生控制信號,并允許它補償PVT的變化。在Stratix III FPGA中有4個DLL,它們都位于器件的邊角,目的是使每個DLL能夠覆蓋器件的兩側,從而可以在器件的各個邊上支持多種DDR3 SDRAM存儲器接口。

跨越高速數據率域和設計簡化

DDR捕獲寄存器和HDR寄存器支持數據從雙倍數據率域(數據在時鐘的兩個邊沿)安全傳送到SDR域(數據位于頻率相同的時鐘的上升沿,但數據寬度加倍),再到HDR域(數據位于時鐘的上升沿,數據寬度仍是加倍,但時鐘頻率僅是SDR域的一半),這樣使得內部設計時序更容易實現。

裸片、封裝和數字信號完整性改進

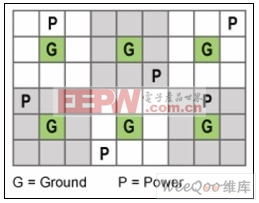

FPGA裸片和封裝的設計必須為高性能的存儲器接口提供更好的信號完整性(即用戶I/O與地和電源的比例為8:1:1,并具有最佳的信號返回路徑,如圖3所示)。此外,FPGA應該提供動態OCT和可變的偏移率,以便能夠控制信號的上升和下降時間以及可編程驅動能力,從而滿足所用標準(即SSTL 1.5 Class II)的要求。

圖3:連接到每個電源和地的8個用戶I/O。

本文小結

高性能Stratix III FPGA可以通過提供高存儲器帶寬、改進的時序余量以及系統設計中的靈活性來彌補高性能DDR3 SDRAM DIMM的不足。由于DDR3在實際使用中將很快超過DDR2,故提供更低成本、更高性能、更高密度和優異的信號完整性的高端FPGA必須提供與JEDEC兼容的讀寫均衡功能,以便與高性能的DDR3 SDRAM DIMM相接。FPGA與DDR3 SDRAM的有機整合將能夠滿足目前和下一代通信、網絡以及數字信號處理系統的要求。

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論