使用賽靈思Vivado設計套件的九大理由

優勢包括:

本文引用地址:http://www.j9360.com/article/185311.htm ♦ 在設計過程中,能夠在外設上完成簡單的讀/寫操作

♦ 無需重新編譯就能將測試模式寫入存儲器

♦ 通過AXI接口能夠測試和校正IP核

♦ 能夠檢查任何AIX外設設備內的數據

集成串行I/O分析器

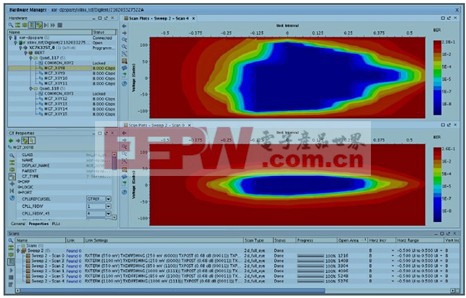

Vivado串行I/O分析器為基于FPGA的系統設計中日漸常用的高速串行I/O通道提供了一種快速、便捷的互動式設置調試方法。Vivado串行I/O分析器能夠在串行I/O通道運行期間對多種高速串行I/O通道進行誤碼率(BER)測試,并實時調整高速串行收發器的參數。這款基于鏈路的Vivado串行I/O分析器,能夠將系統中任何收發器的發射器(TX)連接到任何收發器的接收器(TX)。此外發射器和接收器無需采用相同的SerDes架構。Vivado串行I/O分析器還能夠自動檢測各條鏈路,讓開發人員創建定制鏈路,執行2D眼圖掃描并實時掃描收發器參數(如圖11所示)。

圖11:Vivado串行I/O分析器

理由九:采用C、C++和SystemC語言將驗證速度提高100倍以上

如前文所討論的,Vivado設計套件系統版本內置Vivado HLS,可幫助用戶的設計團隊用C、C++和SystemC語言迅速完成算法設計的創建與迭代工作,同時還在驗證工作中發揮這些高級編程語言的高仿真速度優勢。使用Vivado HLS定點和業界標準浮點math.h庫,開發人員運用C函數規范即可快速為設計建模并完成設計迭代,然后僅根據時鐘周期和吞吐量等考慮因素建立目標感知的RTL架構。將C、C++和SystemC語言用作初始設計和建模語言可極大地加快仿真速度(比RTL仿真速度快數千倍)。在一個視頻設計實例中,10個經處理的視頻幀的仿真速度采用C語言比采用HDL快12,000倍,如表2所示。

表2:Vivado設計套件的視頻設計仿真速度快1.2萬倍

|

輸入 |

RTL仿真時間 |

C語言仿真時間 |

速度提升 |

|

10幀視頻數據 |

約2天 |

10秒 |

約12,000倍 |

總結

賽靈思Vivado設計套件是一種以IP和系統為中心的、領先一代的全新SoC增強型開發環境,用于解決系統級集成和實現工作中的生產力瓶頸問題。這套設計工具專為系統設計團隊開發,旨在幫助他們在更少的器件中集成更多系統功能,同時提升系統性能,降低系統功耗,減少材料清單(BOM)成本。

Vivado設計套件由于如下九大理由,是幫助您實現上述這些目標的理想系統設計工具:

♦ Vivado設計套件可讓用戶進一步提升器件密度。

♦ Vivado設計套件可提供穩健可靠的性能,降低功耗以及可預測的結果。

♦ Vivado設計套件可提供無與倫比的運行時間和存儲器利用率。

♦ Vivado HLS能夠讓用戶用C、C++或SystemC語言編寫的描述快速生成IP核。

♦ Vivado設計套件借助MathWorks公司提供的Simulink和MATLAB工具可支持基于模型的DSP設計集成。

♦ Vivado IP集成器突破RTL的設計生產力制約。

♦ Vivado集成設計環境為設計和仿真提供統一集成開發環境。

♦ Vivado設計套件提供綜合而全面的硬件調試功能。

♦ Vivado HLS使用C、C++或CSystem語言可將驗證速度提高100倍以上。

您的設計團隊不妨立即試試Vivado設計套件,體驗一下其帶來的強大優勢?

c++相關文章:c++教程

評論