使用賽靈思Vivado設計套件的九大理由

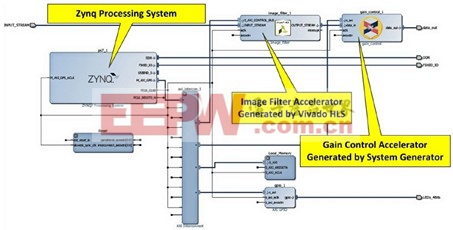

圖8顯示的是系統級設計在Vivado IP集成器中的視圖,這個系統采用了一個賽靈思Zynq-7000處理系統、Vivado HLS生成的圖像濾波器加速器和一個用Vivado System Generator for DSP生成的增益控制加速器。

本文引用地址:http://www.j9360.com/article/185311.htm

圖8:用Vivado HLS和System Generator加速器完成的Zynq設計

Zynq-7000處理系統 Vivado HLS生成的圖像濾波器加速器

System Generator生成的增益控制加速器

加速系統驗證

理由七:用于設計和仿真的Vivado集成設計環境

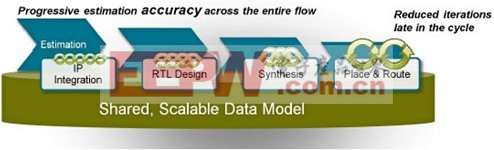

Vivado設計套件還提供完整的全集成成套工具,用于在先進的集成設計環境(IDE)中完成設計輸入、時序分析、硬件調試和仿真工作。Vivado設計套件的集成設計環境的這種設計分析功能采用共享的可擴展數據模型,以容納超大型All Programmable器件。Vivado設計套件在整個設計流程中使用這一單一的數據模型,讓設計團隊能夠盡早在整個設計流程中隨時掌握時序、功耗、資源利用率、路由擁塞等關鍵設計指標。估算也會隨著設計流程的推進越來越準確,從而在減少設計迭代次數的同時推動更快完成設計收斂。

圖9:VIVADO設計套件在整個設計流程中至始至終使用一個共享的可擴展數據模型

Vivado設計套件是唯一在自身的集成設計環境中提供混合語言仿真器的設計解決方案。而同類競爭仿真器的用戶必須或選擇VHDL仿真,或選擇Verilog仿真。對集成眾多廠商提供的IP的最新系統設計來說,混合語言仿真器至關重要。

Vivado設計套件的仿真和調試使用相同的波形觀測儀,這樣可以避免從仿真環境切換到硬件調試環境后還需要重新學習。競爭解決方案往往迫使用戶學習和使用不同波形的工具來完成相同工作。在仿真功能和調試功能全集成的情況下,設計團隊能夠更快地完成工作,且避免出錯,使用Vivado設計套件就是這種情況。

類似地,同類競爭開發工具的交叉探測功能呈碎片化且極度有限。此外這些交叉探測功能一般局限于某種單一的工具。與此對比鮮明的是,Vivado設計套件提供的全面、集成式front-to-back交叉探測功能,適用于所有不同設計視圖,諸如實現設計、綜合設計、時序報告,甚至還可追溯到設計團隊的原始RTL代碼。

由于Vivado設計套件使用單一數據模型架構,所以可在各種設計資源、原理圖視圖、層級瀏覽器、設計報告、消息、布局規劃和Vivado器件編輯器(Vivado Device Editor)之間進行大范圍交叉探測。借助這種獨特的功能,可以即時反饋整個系統開發過程中發現的任何設計問題,從而加快調試,快速完成時序收斂。

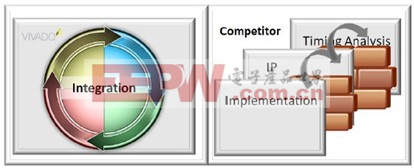

此外,競爭性設計解決方案使用多個磁盤文件用于工具間通信。使用多個磁盤文件帶來的復雜性和低效率不僅會降低工具性能,而且還會造成多重接口,從而顯著增大工具間溝通不暢的幾率。然而,Vivado設計套件則不存在這種問題。它采用單一的共享數據模型處理設計的各方面工作,如圖10所示。

圖10:Vivado設計套件的單一共享數據模型平滑地集成各類設計工作

同類競爭設計解決方案 時序分析

集成 IP

實現

理由八:綜合而全面的硬件調試

Vivado設計套件的探測方法直觀、靈活、可重復。設計人員可選擇最適合自己設計流程的探測策略:

♦ RTL設計文件、綜合設計和XDC約束文件

♦ 網表插入

♦ 用于自動運行探測的互動式TCL或腳本

先進的觸發器和采集功能

Vivado設計套件為檢測復雜事件提供先進的觸發器和采集功能。在調試進程中所有的觸發器參數均可使用,用戶可以實時檢查或動態修改參數,且無需重新編譯設計。

Zynq SoC支持處理器系統(PS)與可編程邏輯(PL)之間交叉觸發

Vivado設計套件還支持Zynq-7000 All Programmable SoC器件內處理器系統(PS)與可編程邏輯(PL)之間的交叉觸發。有了這項功能,結合使用賽靈思軟件開發套件(SDK)、Vivado IP集成器和Vivado邏輯分析器(Vivado Logic Analyzer),可以協同調試同時使用Zynq處理器系統和可編程邏輯的嵌入式設計。再搭配強大的軟件調試器GNU Debugger(GDB)實用工具,設計人員使用Vivado IP集成器和Vivado邏輯分析器可以同步調試軟/硬件算法。Zynq-7000 All Programmable SoC平臺和賽靈思ILA(集成邏輯分析器)IP核間提供有特定的接口信號,可支持無縫協同調試操作。

實現硬件實時讀/寫操作 — JTAG to AXI Master

Vivado設計套件可在硬件調試過程中實時地完成Zynq處理器系統和可編程邏輯間的讀/寫事務處理。最新調試IP核(JTAG to AXI Master)與簡便易用的IP Integrator流相結合,能夠在設計中訪問任何基于AXI的IP模塊中的數據。

c++相關文章:c++教程

評論