使用賽靈思Vivado設計套件的九大理由

注:如圖2所示,同類競爭工具的結果的平均變動要比使用Vivado設計套件得到的結果大四倍。另外,值得注意的是同類競爭解決方案在填滿器件時,可用性能下降了一半。與此形成鮮明對比的是,Vivado設計套件在受測的不同設計上得到的結果一致,性能保持穩定。最后還需要注意是同類競爭解決方案不能處理Vivado設計套件能夠成功處理的大型系統。同類競爭解決方案很快就不堪重負。

本文引用地址:http://www.j9360.com/article/185311.htm

圖2:以復制次數為標準的性能對比

Vivado降低系統功耗

Vivado設計套件提供了業界一流的系統功耗分析與優化工具。從架構或器件選擇階段開始,設計人員就可以運用準確且易用性無與倫比的Xilinx Power Estimator(XPE,賽靈思功耗評估器)電子數據表來確定系統功耗。設計人員不僅能夠通過XPE的快速 評估(Quick Estimate)和IP向導輕松入門,而且還能夠簡單并排比較多種實現方案,幫助設計團隊微調設置,以便地為各種場景精確建模。

當設計進入編譯階段,Vivado設計套件繼續提供準確的功耗分析和估算。Vivado設計套件開箱即用,能夠在不給系統設計的時序造成負面影響的情況下自動降低設計的功耗。如果用戶還需要進一步降低功耗,可以使用Vivado設計套件獨有功能,充分利用賽靈思7系列精細粒度時鐘門控技術,進一步降低整個系統設計或部分設計的功耗。

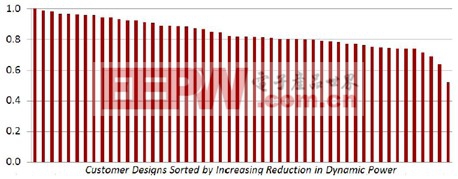

這種Vivado設計套件實現的智能時鐘門控優化技術能夠平均降低動態功耗18%,如圖3所示。

Vivado設計套件提供了一系列無與倫比功能與特性,可幫助用戶輕松完成對設計的分析工作。用戶可以甄別出功耗最大的模塊,從而明確從哪些模塊切入,高效而明顯降低系統功耗。所有這些功能都內置在通用Vivado集成設計環境(IDE)中,所以設計團隊僅借助一款統一的工具套件,就可一次性最小化系統功耗。

系統功耗是設計大多數產品時應考慮的一個重要因素,Vivado設計套件提供的領先一代設計工具是對賽靈思All Programmable器件的有力補充和完善。

圖3:運用智能時鐘門控優化實現的動態功耗比率(按動態功耗降幅分類)

理由三:Vivado設計套件提供了無與倫比的運行時間和存儲器利用率

從設計人員生產力考慮,設計工具應能夠快速運行,最好是快到每天能夠完成多次編譯,這樣設計團隊就能夠迅速得到最終設計。從一開始Vivado設計套件就是為高速運行設計的,比同類競爭的可編程邏輯設計工具的速度明顯要快得多。

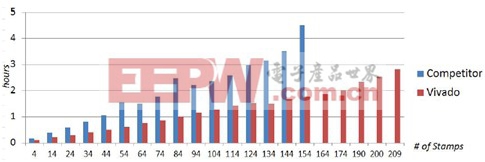

同樣以之前討論過的OpenCores以太網MAC模塊設計為例。圖4說明,隨著實例數量的增加,Vivado設計套件的運行時間比競爭對手的軟件快三倍。此外,數據還表明,Vivado的運行時間的增減可以預測,即運行時間只單調地隨設計規模增減。與此形成鮮明對比的是,同類競爭軟件的運行時間無規律性。例如94個實例的設計完成的速度比使用84個實例的設計快。

圖4:運行時間比較

Vivado內存占用更小

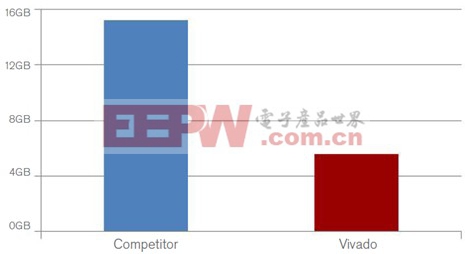

Vivado設計套件采用先進高效的數據模型和結構,內存占用極小且明顯低于同類競爭解決方案的內存占用。此處仍以OpenCores以太網MAC模塊為例。要成功運行規模最大的設計(154個實例),競爭軟件需要占用16GB的RAM,相比之下運行同樣規模大小的設計,Vivado設計套件占用的內存要小三分之二(見圖5)。內存占用減少意味著Vivado設計套件擁有明顯的生產力優勢,因為設計人員在編譯較大型系統設計時不會耗盡內存。

圖5:內存占用

加快系統集成

理由四:使用Vivado高層次綜合生成基于C語言的IP

如今的無線、醫療、軍用和消費類應用均比以往更加尖端,使用的算法也比以往更加復雜。業界算法開發的金標準就是采用C、C++和SystemC高級編程語言。過去設計流程中需要經過一個緩慢且容易出錯的步驟來將用C、C++或SystemC語言編寫的算法轉換為適合于綜合的Verilog或VHDL硬件描述。而現在Vivado設計套件系統版本中提供的Vivado高層次綜合功能可輕松地自動完成這一步驟。

c++相關文章:c++教程

評論