合成孔徑雷達成像系統逆存儲轉置器的DSP設計

摘要:逆存儲轉置器(ICTM)是合成孔徑雷達(SAR)實時成像處理系統的一個重要模塊。本文設計的ICTM模塊以TI的一款高性能定點DSP芯片TMS320C6415為核心處理器,兩條大容量SDRAM作為外部存儲器,實現輸入數據的逆存儲轉置操作。軟件編程采用并行處理方式,提高了代碼執行效率。實際運行表明,模塊能充分滿足成像系統的實時性要求,同時其強大的處理能力也為今后處理更多的數據預留了空間。

關鍵字:TMS320C6415;合成孔徑雷達;逆存儲轉置器

1.引言

合成孔徑雷達成像系統是一種全天時、全天候的高分辨率主動微波遙感成像系統,在地理遙感、地形測繪、災情預測和軍事偵察等領域有著重要應用。逆存儲轉置器(ICTM)是合成孔徑雷達成像系統的一個重要模塊,它需要將上位機方位壓縮模塊輸出的圖像數據以方位線的形式依次寫入外部存儲器,通過數據的逆轉置處理,以距離線的形式將圖像數據依次輸出。此外,ICTM的輸出數據將經過數據I/O節點發送到下位機圖像顯示模塊,使圖像顯示模塊能實時的以距離線形式滾動顯示雷達圖像。ICTM以TI的一款高性能定點DSP芯片TMS320C6415為核心處理器,兩條大容量SDRAM作為外部存儲器,實現輸入數據的逆存儲轉置操作,同時其強大的處理能力也為今后處理更多的數據提供了升級空間。

2.TMS320C6415芯片簡介

TMS320C6415是TI公司生產的高性能定點DSP C6000系列中的一款,該系列的DSP都是基于VelociTITM架構的VLIW DSP,在每個時鐘周期內可以執行8條32bit的指令。C6415的核心工作頻率最高可以達到720MHz,峰值工作速率為5.76GIPS。C6415提供與SDRAM的無縫接口,可以有效的簡化硬件設計開發難度,利用C6415的片選空間映射管理SDRAM,最多可以支持1GB的外部存儲空間,完全可以滿足逆存儲轉置處理所需的192M存儲要求。

TMS320C6415的CPU結構具有2個通道,每個通道有4個功能單元(1個乘法器和3個算術邏輯單元),16個32位通用寄存器,每個通道的功能單元可以隨意訪問本通道的寄存器。CPU還有2個交叉單元,通過它們,一個通道的功能單元可以訪問另一個通道的寄存器。另外,CPU還具有256bit寬的數據和程序通道,可以使程序寄存器在每個時鐘周期提供8條并行執行指令,這種CPU結構是DSP具有VLIW結構的基本條件。

DSP的存儲空間映射為內部存儲器、內部外設及外部擴展存儲器,其中內部存儲器由64KB內部程序存儲器和數據存儲器構成。內部程序存儲器可以映射到CPU地址空間或者作為Cache操作。內部和外部數據存儲器均可以通過CPU、DMA或HPI(Host Interface)方式訪問,HPI接口使上位機可以訪問DSP的存儲空間。

3.ICTM工作原理

ICTM模塊的主要功能是將上位機方位壓縮模塊輸出的數據重新排列順序,使得依次沿方位向排列的數據變換成沿距離向排列,使下位機圖像顯示模塊能實時滾動顯示圖像。

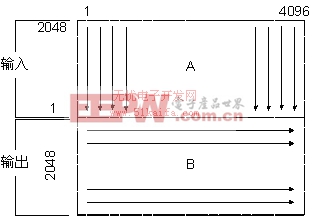

圖1 ICTM模塊工作原理示意圖

ICTM模塊的工作原理可用圖1來表示。整個SDRAM存儲空間劃分為BANKA和BANKB兩塊存儲區,兩塊BANK的列深度為輸入的方位向點數2048點,行深度為輸出的距離向點數4096點,為使兩塊BANK的讀/寫數據量平衡,需要在每個工作周期內輸入兩條方位線(22048點)數據,同時輸出一條距離線(14096點)數據。兩塊存儲區采用“乒乓”操作的讀寫方式,即如果等間隔讀BANKA區域,則連續寫BANKB區域,反之如果連續寫BANKA區域,則等間隔讀BANKB區域,讀完一塊存儲區的同時,另一塊存儲區也剛好寫滿。這樣兩塊存儲區交替工作,充分節約了讀/寫SDRAM的時間開銷,有利于滿足整個系統的實時性要求。

4.ICTM硬件電路設計

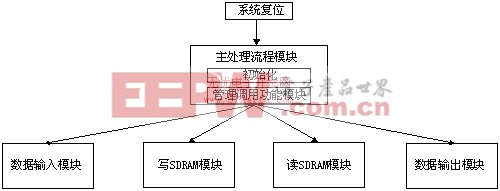

圖2 ICTM模塊硬件電路結構示意圖

ICTM模塊的硬件電路設計框圖如圖2所示。根據ICTM模塊的工作需要,主存儲器采用兩頁式工作結構,每頁集成256MBytes大小的SDRAM,分別配置在C6415的兩個CE空間。SDRAM和作為輸入/輸出緩存的同步FIFO都連接在C6415 64Bit位寬的EMIFA接口,以保證較高的數據傳輸帶寬。

4.1 SDRAM存儲電路

主存儲器類型選擇為SDRAM,即標準的144pin筆記本內存條(標準SODIMM封裝),目前選用256M容量大小。由于ICTM模塊的SDRAM接口采用可擴充接法,因此可以擴充到512MB容量。即如果SDRAM Module的容量為256MB,則列地址為A0~A8 ,如果SDRAM Module容量為512MB,則列地址為A0~A9。DSP的EMIFA口CE0、CE1輸出信號分別接SDRAM的BANK選擇管腳S0、S1。即如果SDRAM的BANK只有一個,則只有S0有效,這樣SDRAM只占用DSP的EMIFA口CE0空間,如果SDRAM的BANK有兩個,則占用DSP的EMIFA口CE0、CE1空間。

4.2 輸入/輸出FIFO

DSP的EMIFA口CE2/CE3空間分別控制輸入FIFO和輸出FIFO。輸入FIFO采用IDT公司的IDT72V3670(8K36Bit),輸出FIFO采用IDT公司的IDT72V3680(16K36 Bit),封裝形式為TQFP,128pin。FIFO的設計采用同步方式讀寫,但是利用0Ω電阻等效的短接線設計方式,也可以工作在異步模式下,FIFO控制信號通過CPLD做譯碼。

ICTM模塊用于讀寫操作的64bit FIFO采用用兩個32bit的FIFO并連實現,利用FIFO深度來做等效的輸入、輸出“乒乓”操作。其中輸出只用到一片FIFO,另外一片為將來大數據量的處理預留空間。

4.3 CPLD和HPI

ICTM模塊各功能單元的電路狀態、時序控制以及I/O接口控制都由CPLD完成。此外,通過C6415的主機接口(HPI)可以直接訪問DSP映射管理下的所有片內和片外存儲單元。因此,在電路設計中將DSP的HPI接口通過CPLD與系統控制總線相連,從而使主控能夠直接訪問DSP的HPI接口,進而滿足處理程序實時下載和指令數據實時傳輸的要求。

ICTM模塊的硬件設計充分考慮了結構化的設計要求,為合成孔徑雷達實時成像處理系統提供了高性能的逆存儲轉置硬件平臺,結合配置的控制軟件就可以實現實時成像處理所需的逆存儲轉置功能。

5.軟件設計與實現

TMS320C6415是面向C結構的DSP芯片,支持標準C/C++編程,其開發工具Code Composer Studio(CCS2.21)內嵌C編譯器的編譯效率可達匯編的85%。另外,C編程可提高DSP程序的可維護性、可移植性、可繼承性,便于縮短軟件開發周期,因此本DSP程序選擇采用C語言編寫。

圖3 程序層次結構和模塊劃分

5.1軟件模塊劃分

軟件層次結構和模塊劃分如圖3所示。DSP軟件的主要部分是底層的四個功能模塊,這四個功能模塊分別完成以下操作:1. 從輸入FIFO中讀取兩條方位線數據(每條方位線2048點,每點數據類型為短整型)到DSP內存中;2. 將讀入的數據按順序存儲到SDRAM中;3. 把SDRAM中的數據沿距離線順序讀到DSP內存中,即完成轉置操作;4. 把轉置后的數據送至輸出FIFO。

5.2軟件各模塊間關系

l 上電初始化模塊:在DSP上電后,完成與硬件工作有關的各控制寄存器的初始化,以及與軟件工作有關的各內部變量和存儲區的初始化;

l 主處理模塊:調用其它功能模塊,完成整個逆存儲轉置流程;

l 數據輸入模塊:受主處理模塊調用,利用EDMA完成數據輸入;

l 寫SDRAM模塊:受主處理模塊調用,利用EDMA完成數據寫操作;

l 讀SDRAM模塊:受主處理模塊調用,利用EDMA完成數據讀操作;

l 數據輸出模塊:受主處理模塊調用,利用EDMA完成數據輸出。

5.3 C6415的EDMA控制寄存器

EDMA是C621x/671x/641x特有的數據存取方式。在C621x/671x/641x中,EDMA控制寄存器負責片內二級存儲器與其它外設之間的數據傳輸。EDMA控制寄存器和DMA控制寄存器在結構上有很大不同。其增強之處包括:

l 提供了64個傳輸通道;

l 通道間優先級可設置;

l 支持不同結構數據傳輸的鏈接。

EDMA控制寄存器主要由事件(中斷)處理寄存器、事件編碼器、參數RAM以及硬件地址發生器構成。其中,事件(中斷)處理寄存器負責對EDMA事件進行捕獲。一個事件相當于一個同步信號,由它觸發一個EDMA通道開始數據傳輸。如果多個事件同時發生,則由事件編碼器對它們進行分辨,將同時發生的事件進行排序,并決定事件的處理順序。EDMA的參數RAM中存放了有關的傳輸參數,這些參數會被送往硬件地址發生器,進而產生讀寫操作所需的地址。

5.4 ICTM軟件設計流程

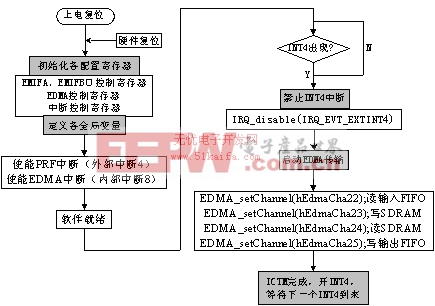

圖4 ICTM軟件設計流程

ICTM模塊軟件設計流程可用圖4來表示。首先完成上電復位,初始化EMIFA和EMIFB配置寄存器、中斷控制寄存器和EDMA控制寄存器,之后在主程序中完成各常量和變量的定義及初始化。完成上述初始化定義后就可以使能外部中斷控制寄存器和EDMA控制寄存器,等待外部中斷INT4的觸發。INT4的觸發源來自脈沖PRF,該脈沖的到來說明兩條待輸入的方位線數據已送至輸入FIFO,此時CPU可以將這兩條方位線數據讀到DSP內存,并送至SDRAM的相應存儲區。

由于輸入/輸出數據結構相對簡單,讀輸入FIFO、寫SDRAM、讀SDRAM以及寫輸出FIFO四個過程可以采用“EDMA鏈(EDMA Chain)”的方式進行。即第一個EDMA傳輸完成后,緊接著啟動第二個EDMA傳輸,直到最后一個EDMA傳輸完成,這樣可以在不受CPU干預的情況下完成數據的搬移,有利于提高數據傳輸效率。

5.5 軟件并行設計問題

由于EDMA不受CPU干預,因此在使用EDMA傳輸數據的同時,CPU可并行執行其它指令,這樣可極大提高代碼的執行效率。舉例如下:

if(EDMA_intTest(22))

{

*ifoeoff=0;

EDMA_intClear(22);

EDMA_setChannel(hEdmaCha25);// trigger EDMA to reading data from SDRAM

#pragma MUST_ITERATE(32,,8);

for(i=0;i64;i++)

{

headwriteaddr[i]=inputa[i];

}

WORD_ALIGNED(inputb);

WORD_ALIGNED(inputc);

WORD_ALIGNED(inputa);

#pragma MUST_ITERATE(64,,8);

for(i=0;i4096;i++)

{

inputb[i]=inputa[2*i+64];

inputc[i]=inputa[2*i+65];

}

}

其中EDMA_setChannel(hEdmaCha25)語句用來啟動EDMA25通道的傳輸,完成從SDRAM讀取轉置數據的任務。EDMA在進行數據傳輸的同時,CPU則繼續執行之后的三條語句headwriteaddr[i]=inputa[i]、inputc[i]=inputa[2*i+65]、inputb[i]=inputa[2*i+64],直到EDMA傳輸完成并發出中斷,CPU才響應EDMA中斷。

顯然,采用上述并行處理的方式,CPU工作周期得到充分利用,提高了代碼的執行效率,有利于滿足系統的實時性要求。

6.結束語

逆存儲轉置器(ICTM)是合成孔徑雷達(SAR)實時成像處理系統的一個重要模塊。本文選擇TI的一款高性能定點DSP芯片TMS320C6415為核心處理器,兩條大容量SDRAM作為外部存儲器,實現輸入數據的逆存儲轉置操作。軟件編程采用并行處理方式,提高了代碼執行效率。單板測試和系統聯調表明,設計的逆存儲轉置器滿足各項性能指標,已通過項目組驗收,即將投入實際應用。

參考文獻

1. 李方慧,王飛等,TMS320C6000系列DSPs原理與應用(第2版),電子工業出版社,北京,2003.1

2. 譚浩強,C程序設計,清華大學出版社,北京,1991.7

評論