Xilinx UltraScale?:為您未來架構而打造的新一代架構

因此,基于UltraScale架構的All Programmable器件能提供超過1 Tb/s的DDR SDRAM存儲器帶寬,用以滿足領先的新一代系統設計提出的海量數據流、快速處理和超大存儲器等要求。與軟核PHY相比,硬化的SDRAM PHY模塊能將讀取時延降低30%,同時該模塊能控制DDR4 SDRAM,從而將用于外部存儲器的功耗降低20%以上。

本文引用地址:http://www.j9360.com/article/147542.htm片上Block RAM性能往往是影響系統最大時鐘速率的關鍵因素。賽靈思已對UltraScale架構All Programmable器件中的Block RAM進行了重新設計,以便在降低功耗的同時與系統中其他可編程模塊的性能相匹配。新的Block RAM架構支持高速存儲器級聯,消除了DSP和包處理中存在的瓶頸。輸出多路復用器在這種新架構中的使用方式很獨特,使得Vivado設計套件工具在無需附加片讓布線或邏輯資源的情況下也能高效創建大型、快速的RAM陣列和FIFO。

賽靈思還加強了基于UltraScale架構的Block RAM FIFO配置,以便在相同FIFO上支持不同寬度的輸入與輸出端口。當FIFO需要從一個系統時鐘域跨越到另一個域時(UltraScale架構現在支持很多個時鐘域),這項功能很有幫助。

實現快速、智能處理

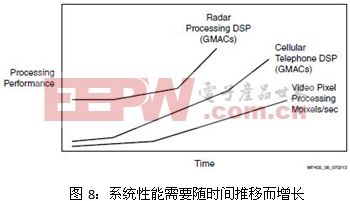

為滿足最終用戶要求,DSP和包處理系統的性能需要不斷提高,如圖8示。

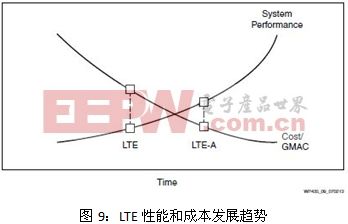

人們需要從噪聲中提取更多信號信息;需要創建更加逼真的圖像;需要應對無止境的數據包流量增長,所有這些都在對性能提出更高要求。然而,與此同時,還要將成本控制在規定的預算范圍內,這樣就給設計帶來了諸多實際限制。如圖9所示,圖中描述了LTE和LTE Advanced(LTE-A)基站的性能與成本隨時間的變化趨勢。

簡而言之,客戶需要以更低成本獲得更高的系統性能,這是大多數電子產業永恒不變的趨勢,而這也正是UltraScale架構的優勢所在。

在領先的性能優勢基礎之上增強DSP

賽靈思針對UltraScale架構顯著增強了已經具備行業最高性能的Virtex-7 FPGA的DSP48E1 DSP slice,以實現更快的數字信號處理能力,同時減少DSP模塊外部的布線或邏輯資源使用量。在DSP slice上應用的一系列創新功能可以改善乘法運算和MACC運算,從而增強功能并降低功耗。

基于UltraScale架構的DSP48E2 DSP slice包含27×18位乘法器,可將更大的函數映射到更少的DSP slice中。例如,DSP48E2 block憑借更寬的27×18位乘法器能夠以更少的資源實現IEEE Std 754雙精度算法,與采用賽靈思7系列All Programmable器件中的DSP48E1模塊實現相同功能相比,所采用的DSP模塊數量可減少三分之二。

在DSP48E2 slice中包含寬MUX和寬XOR函數后,像錯誤校正與控制(ECC)、循環冗余校驗(CRC)以及前向糾錯(FEC)等非DSP運算就可以將DSP slice作為高速、硬化的寬邏輯模塊來使用。這些增強特性有助于提高性能,降低功耗,并減少可配置邏輯模塊(CLB)的使用量,從而將更多CLB用于實現其他功能。正是通過為DSP等模塊增加新功能,UltraScale架構得以同時滿足新一代應用對于提高處理能力以及降低成本方面的要求。

擴展的智能數據包處理性能

無止境的帶寬需求正持續推高網絡通信基礎設施的升級投入。數字視頻傳輸所形成的海量數據流加速了100Gb/s網絡設備的成熟,同時也加大了對400G解決方案的需求。數據包處理甚至可以給當前業內數百Gb每秒速率的最先進架構帶來嚴峻的性能挑戰。在線路速度下執行的校驗和計算與橋接等基礎數據包處理功能會對性能和資源利用率帶來顯著影響。

除了解決與高性能數據包處理有關的海量數據流問題外,UltraScale架構還包含多種專為數據包處理定制的創新功能。其中包括:對DSP48模塊進行修改以支持線速度下進行的CRC 32校驗和計算;加入了硬化的Gb以太網MAC和Interlaken芯片到芯片接口,用以支持智能數據包處理的性能突破和最新的集成等級。

存儲器相關文章:存儲器原理

評論