摘要本文介紹了一種在FPGA中實現的增強型正交頻分復用(OFDM)調制器設計,它使用了逆FFT模式的萊迪思快速傅立葉變換(FFT)Compiler IP核和萊迪思有限脈沖響應(FIR)濾波器IP核。該設計解決了在沒有主控制器的情況下生成復雜測試模式的常見難題,大大提高了無線鏈路測試的效率。通過直接測試模擬前端的JESD204B鏈路,OFDM調制器擺脫了對主機控制器的依賴,簡化了初始調試過程。該設計可直接在萊迪思FPGA核中實現,從而節省成本并縮短開發周期。該調制器的有效性驗證中使用了Avant-X70 V

關鍵字:

萊迪思半導體 iFFT FIR IP 5G OFDM

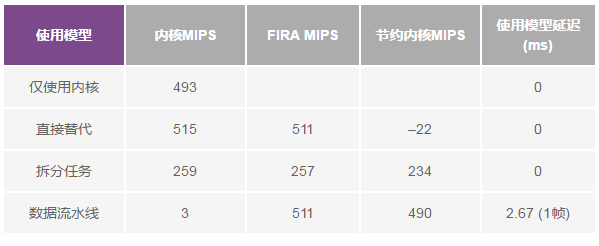

有限脈沖響應(FIR)和無限脈沖響應(IIR)濾波器都是常用的數字信號處理算法——尤其適用于音頻處理應用。因此,在典型的音頻系統中,處理器內核的很大一部分時間用于FIR和IIR濾波。數字信號處理器上的片內FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔FIR和IIR處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。圖1.FIRA和IIRA系統方框圖。圖1顯示了FIRA和IIRA的簡化方框圖,以及它們

關鍵字:

ADI FIR IIR

摘要有限脈沖響應(FIR)和無限脈沖響應(IIR)濾波器都是常用的數字信號處理算法---尤其適用于音頻處理應用。因此,在典型的音頻系統中,處理器內核的很大一部分時間用于FIR和IIR濾波。數字信號處理器上的片內FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔FIR和IIR處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。圖1.FIRA和IIRA系統方框圖簡介圖1顯示了FIRA和IIRA的簡化方框圖,

關鍵字:

RAM TCB FIR

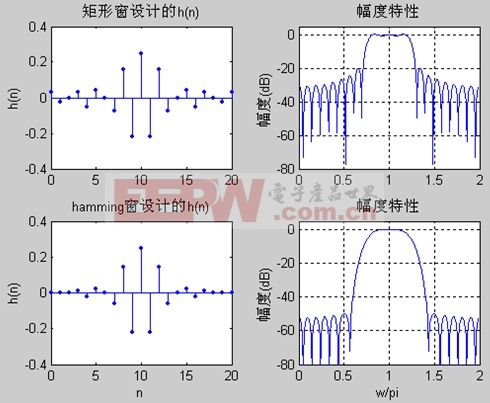

數字濾波器廣泛應用于硬件電路設計,在離散系統中尤為常見,一般可以分為FIR濾波器和IIR濾波器,那么他們有什么區別和聯系呢。 FIR濾波器 定義: FIR濾波器是有限長單位沖激響應濾波器,又稱為非遞歸型濾波器,是數字信號處理系統中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。 特點: FIR濾波器的最主要的特點是沒有反饋回路,穩定性強,故不存在不穩定的問題; FIR具有嚴格的線性相位,幅度特

關鍵字:

FIR IIR

引言

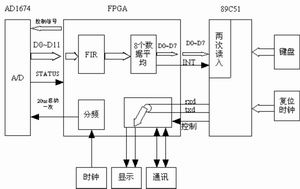

車輛在動態稱重時,作用在平臺上的力除真實軸重外,還有許多因素產生的干擾力,如:車速、車輛自身諧振、路面激勵、輪胎驅動力等,給動態稱重實現高精度測量造成很大困難。若在消除干擾的過程中采用模擬方法濾波,參數則不能過大,否則將產生過大的延遲導致不能實現實時處理,從而造成濾波后的信號仍然含有相當一部分的噪聲。所以必須采用數字濾波消除干擾。

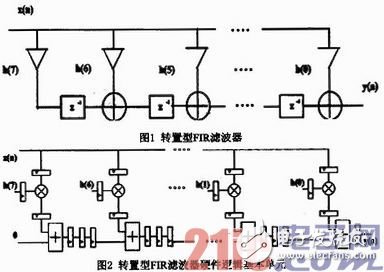

FIR濾波的原理及實現

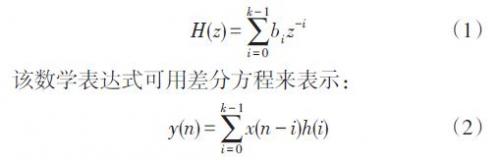

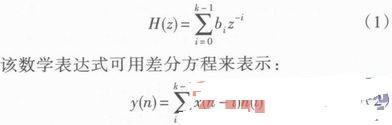

本文采用FIR數字濾波,其原理如公式1所示。

Y(n)= (1)

其中h(k)為系統濾波參數,x(n)為采集的信

關鍵字:

FPGA FIR

簡介:本文提出的方法使得電路層錯綜在一起的路徑按照其不同的時間延遲規則的分離開,關鍵路徑和各種不同延遲的非關鍵路徑對應為不同的模塊,針對不同的路徑長度采取不同的供電電壓。通過剩余數方法[3] 將一個乘法運算化簡為幾個非常簡單的乘法或加法,并將濾波器按照不同的路徑延遲劃分幾個相互獨立的模塊,使之適合采用不同的供電電壓,從而降低功耗。

1 引言

隨著移動及便攜式電子設備的普及和芯片頻率的不斷提高,功耗成為電路設計中必須考慮的重要因素。近來,集成電路設計工具已經逐步支持多電壓設計,因而,使得對適

關鍵字:

FIR

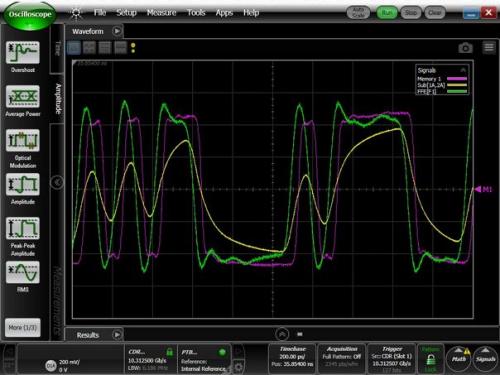

網絡串行解串器(SERDES)的串行數據輸出速度已經高達28Gbps,并且還在繼續發展。在如此高數據速率的條件下,即使很短的PCB走線也會起到傳輸線的作用,進而通過衰減和散射降低信號完整性。在芯片的焊球上監視SERDES發送器輸出信號很難做到。通常信號會引到SMA或SMP連接器后再用示波器進行監測。然而,信號特性會因為IC和連接器之間的傳輸線而發生改變。因此,真正的挑戰是在SERDES引腳處監視信號性能,而這可以通過去除傳輸線效應來實現。本設計實例介紹了一種去除傳輸線的方法。

假設H(s)是走線

關鍵字:

FIR 濾波器

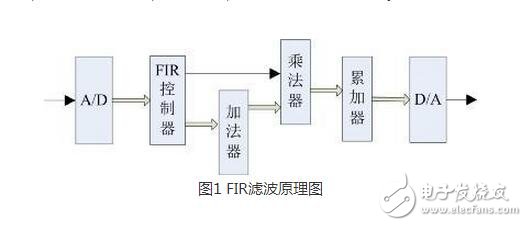

導讀:FIR濾波器是非遞歸型濾波器的簡稱,又叫有限長單位沖激響應濾波器。在數字信號處理系統中較基本的元件,今天帶大家了解FOR濾波器的原理

FIR濾波器原理——特點

FIR濾波器有以下幾點:

Ⅰ、數字濾波器還具有模擬濾波器不能比擬的可靠性。組成模擬濾波器的電子元件的電路特性會隨著時間、溫度、電壓的變化而漂移,而數字電路就沒有這種問題。只要在數字電路的工作環境下,數字濾波器就能夠穩定可靠的工作。

Ⅱ、數字濾波器相比模擬濾波器有更高的信噪比。這主要是因為

關鍵字:

FIR 濾波器 FIR濾波器原理

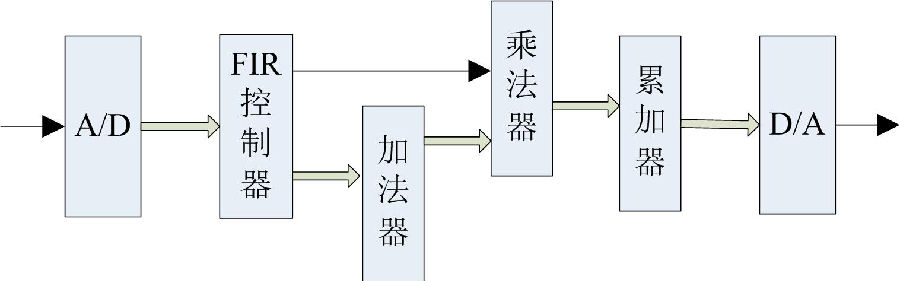

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

具體實現

結構設計

基于抽取濾波器的工作原理,本文采用XC2V1000實現了一個抽取率為2、具有線性相位的3階FIR抽取濾波器,利用原理圖和VHDL共同完成源文件設 計。圖1是抽取濾波器的頂層原理圖。其中,clock是工作時鐘,reset是

關鍵字:

FPGA FIR

FIR濾波器具有幅度特性可隨意設計、線性相位特性可嚴格精確保證等優點,因此在要求相位線性信道的現代電子系統,如圖像處理、數據傳輸等波形傳遞系統中,具有很大吸引力。本文簡單介紹了其線性相位條件和設計方法,并且提供了一種用DSP實現的方法。

一、 引 言

在許多信息處理過程中,如對信號的過濾、檢測、預測等,都要廣泛地用到濾波器,而數字濾波器則因其設計靈活、實現方便等特點而廣為接受。

所謂數字濾波器就是具有某種選擇性的器件、網絡或以計算機硬件支持的計算程序。其功能本質是按事先設計好的程序,

關鍵字:

DSP FIR 數字濾波器

l 引 言

隨著信息技術和計算機技術的飛速發展,數字信號處理技術在眾多領域得到廣泛應用。數字濾波器由于其精度高、穩定性好、使用靈活等優點,廣泛應用在各種數字信號處理領域。數字濾波器根據沖擊響應函數的時域特性,可以分為FIR(有限長沖擊響應濾波器)和IIR(無限長沖擊響應濾波器)。FIR濾波器與IIR濾波器相比,具有嚴格的線性相位,幅度特性可任意等優點。而且,FIR濾波器的單位抽樣響應是有限長的,故一定是穩定的,他又可以用快速傅里葉變換(FFT)算法來實現過濾信號,可大大提高運算效率。

Ma

關鍵字:

Matlab DSP FIR 數字濾波器

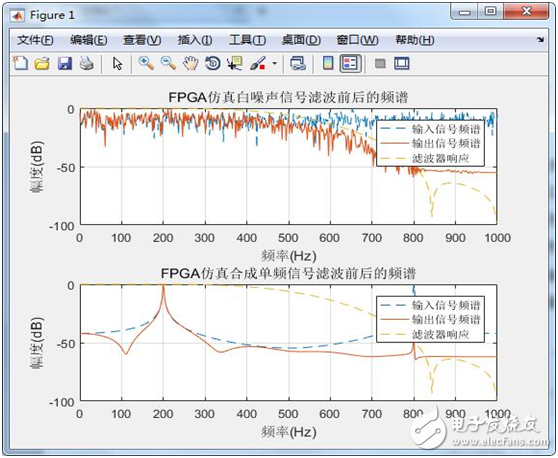

0.引言

FIR(Finite Impulse Response,有限沖擊響應)數字濾波器具有穩定性高、可以實現線性相位等優點,廣泛被應用于信號檢測與處理等領域[1,2]。由于FPGA(Field Programmable Gate Array,現場可編程門陣列)基于查找表的結構和全硬件并行執行的特性,如何用FPGA 來實現高速FIR 數字濾波器成了近年來數字信號處理領域研究的熱點。目前,全球兩大PLD 器件供應商都提供了加速FPGA 開發的IP(IntelligentProperty,知識產權

關鍵字:

IP核 FIR 低通濾波器

實現數字化是控制系統的重要發展方向,而數字信號處理已在通信、語音、圖像、自動控制、雷達、軍事、航空航天等領域廣泛應用。數字信號處理方法通常涉及變換、濾波、頻譜分析、編碼解碼等處理。數字濾波是重要環節,它能滿足濾波器對幅度和相位特性的嚴格要求,克服模擬濾波器所無法解決的電壓和溫度漂移以及噪聲等問題。而有限沖激響應FIR濾波器在設計任意幅頻特性的同時能夠保證嚴格的線性相位特性。利用FPGA可以重復配置高精度的FIR濾波器,使用VHDL硬件描述語言改變濾波器的系數和階數,并能實現大量的卷積運算算法。結合MA

關鍵字:

FPGA FIR 數字濾波器

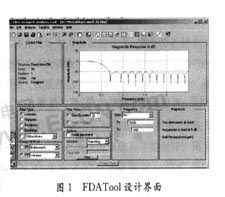

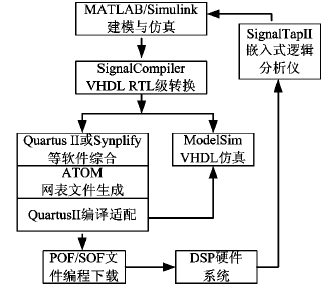

本文簡要介紹了FIR數字濾波器的結構特點和基本原理,提出基于FPGA和DSP Builder的FIR數字濾波器的基本設計流程和實現方案。

在Matlab/Simulink環境下,采用DSP Builder模塊搭建FIR模型,根據FDATool工具對FIR濾波器進行了設計,然后進行系統級仿真和ModelSim功能仿真,其仿真結果表明其數字濾波器的濾波效果良好。通過SignalCompiler把模型轉換成VHDL語言加入到FPGA的硬件設計中,從QuartusⅡ軟件中的虛擬邏輯分析工具SignalT

關鍵字:

FPGA FIR 數字濾波器

引言

數字濾波器是語音與圖像處理、模式識別、雷達信號處理、頻譜分析等應用中的一種基本的處理部件, 它能滿足波器對幅度和相位特性的嚴格要求, 避免模擬濾波器所無法克服的電壓漂移、溫度漂移和噪聲等問題。有限沖激響應(FIR)濾波器能在設計任意幅頻特性的同時保證嚴格的線性相位特性。

1 FIR 數字濾波器

FIR 濾波器用當前和過去輸入樣值的加權和來形成它的輸出, 如下所示的前饋差分方程所描述的。

FIR 濾波器又稱為移動均值濾波器, 因為任何時間點的輸出

關鍵字:

Verilog FIR 數字濾波器

fir介紹

您好,目前還沒有人創建詞條fir!

歡迎您創建該詞條,闡述對fir的理解,并與今后在此搜索fir的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473