基于FPGA 的FIR 數字濾波器設計方案

本文簡要介紹了FIR數字濾波器的結構特點和基本原理,提出基于FPGA和DSP Builder的FIR數字濾波器的基本設計流程和實現方案。

本文引用地址:http://www.j9360.com/article/267746.htm在Matlab/Simulink環境下,采用DSP Builder模塊搭建FIR模型,根據FDATool工具對FIR濾波器進行了設計,然后進行系統級仿真和ModelSim功能仿真,其仿真結果表明其數字濾波器的濾波效果良好。通過SignalCompiler把模型轉換成VHDL語言加入到FPGA的硬件設計中,從QuartusⅡ軟件中的虛擬邏輯分析工具SignalTapⅡ中得到數字濾波器實時的結果波形圖,結果符合預期。

0引言

在信息信號處理過程中,數字濾波器是信號處理中使用最廣泛的一種方法。通過濾波運算,將一組輸入數據序列轉變為另一組輸出數據序列,從而實現時域或頻域中信號屬性的改變。常用的數字濾波器可分為有限脈沖響應(FIR)濾波器和無限脈沖響應(IIR)濾波器兩種。其中,FIR數字濾波器具有嚴格的線性相位,而且非遞歸結構也保證了運算的穩定性。在實時性要求比較高的應用場合,采用可編程芯片FPGA加以實現,相比于DSP芯片或專用芯片的實現方法,具有高速、高精度、高靈活性的優點。本文在采取了一種基于FPGA和DSP Builder的方法設計FIR數字濾波器時,采用了層次化、模塊化的設計思想,遵循DSP Builder的設計開發流程,在Matlab/Simulink中建立模型并進行系統級仿真,再進行Verilog語言轉換,ModelSim仿真驗證無誤后實現了FIR數字濾波器的實時測試。

1 FIR數字濾波器的基本原理及結構

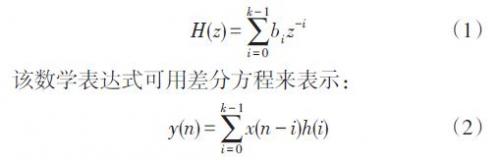

對于一個FIR濾波器系統,它的沖擊響應總是有限長的,其系統函數可以記為:

式中:x(n)是輸入采樣序列;h(i)是濾波器系數;k是濾波器階數;y(n)表示濾波器的輸出序列。

圖1為k階FIR數字濾波器的結構框圖。

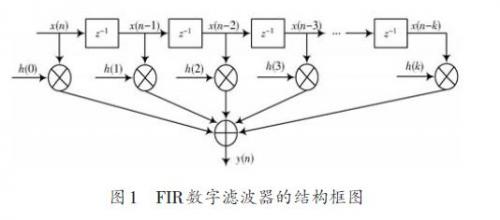

2 FIR數字濾波器的設計流程

該設計流程主要涉及到Matlab/Simulink、DSPBuilder和QuartusⅡ等工具軟件的開發設計。整個設計流程,包括從系統描述直至硬件實現,可以在一個完整的設計環境中完成,如圖2所示。

(1)Matlab/Simulink中設計輸入,即在Matlab的Simulink環境中建立一個擴展名為mdl的模型文件,用圖形方式調用Altera DSP Builder和其他Simulink庫中的圖形模塊(Block),構成系統級或算法級設計框圖(或稱Simulink設計模型)。

(2)利用Simulink的圖形化仿真、分析功能,分析此設計模型的正確性,完成模型仿真,也叫系統級仿真。

(3)DSP Builder設計實現的關鍵一步,通過Signal-Compiler把Simulink的模型文件轉化成通用的硬件描述語言Verilog文件。

(4)轉換好的Verilog源代碼用ModelSim軟件進行功能仿真,驗證Verilog文件的正確性。接下來的幾個步驟是對以上設計產生的Verilog的RTL代碼和仿真文件在QuartusⅡ工具軟件中進行綜合、編譯適配,生成擴展名為。sof的文件加載到FPGA硬件系統中。

3 FIR數字濾波器的詳細設計

3.1 FIR數字濾波器模塊設計與系統級仿真

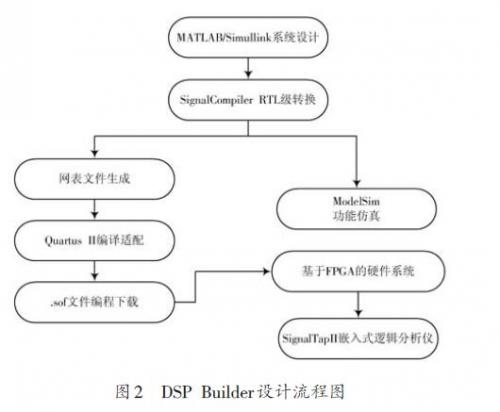

根據FIR數字濾波器的原理,在Simulink環境下搭建16階的FIR數字濾波器結構,如圖3所示。

在模型的搭建過程中,使用了兩個8位的Shift Taps移位寄存器模塊對輸入信號進行分解,然后根據數字濾波器的原理進行算法計算。

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

數字濾波器相關文章:數字濾波器原理

評論