使用萊迪思iFFT和FIR IP的5G OFDM調制用例

摘要

本文引用地址:http://www.j9360.com/article/202504/469494.htm本文介紹了一種在FPGA中實現的增強型正交頻分復用(OFDM)調制器設計,它使用了逆FFT模式的萊迪思快速傅立葉變換(FFT)Compiler IP核和萊迪思有限脈沖響應(FIR)濾波器IP核。該設計解決了在沒有主控制器的情況下生成復雜測試模式的常見難題,大大提高了無線鏈路測試的效率。

通過直接測試模擬前端的JESD204B鏈路,OFDM調制器擺脫了對主機控制器的依賴,簡化了初始調試過程。該設計可直接在萊迪思FPGA核中實現,從而節省成本并縮短開發周期。

該調制器的有效性驗證中使用了Avant-X70 Versa評估板,通過萊迪思JESD204B IP接口鏈路,與亞德諾半導體(ADI)的5G射頻前端評估板ADRV9029進行了互操作性測試。

總之,本文介紹了一種集成了萊迪思FIR和iFFT IP核的新型OFDM調制器設計,簡化了無線鏈路驗證,降低了成本,縮短了開發時間。

1、引言

正交頻分復用(OFDM)是許多無線和有線通信系統,特別是5G和Wi-Fi 4/5/6/7標準中使用的一項關鍵技術。OFDM以其頻譜效率高、抗信道衰落的穩健性和靈活性而著稱。

本文介紹了一種增強型解決方案來解決這些系統中遇到的一個常見問題:對復雜測試模式的需求,而這些模式在沒有主控制器的情況下很難生成。本文介紹了OFDM調制器的設計和實現。這種功能對無線鏈路測試特別有用。?該設計通過集成萊迪思FPGA優化的快速傅里葉變換(FFT)Compiler IP核(逆FFT模式)和有限脈沖響應(FIR)濾波器IP核實現開發。這一方案替代了此前采用HDL Coder生成FIR濾波器和逆FFT模塊的方法,但后者仍不失為一種有效且可靠的解決方案。

萊迪思FFT Compiler IP核提供正向和逆向FFT模式,可配置FFT點數及實現模式,確保信號處理的靈活性和效率。在本設計中,使用了逆向模式FFT Compiler IP核(iFFT)。萊迪思FIR濾波器IP核使用萊迪思器件中的高性能數字信號處理(DSP)模塊來實現。它提供可配置的輸入數據、系數和輸出數據寬度,支持各類廣泛的應用。

本文還討論了在無線鏈路初始啟動過程中遇到的一個常見問題:缺少主控制器而無法將OFDM模式輸入FPGA。如果要使用主機提供OFDM模式,就必須在FPGA和主機之間建立匹配的接口,如PCIe,并在無線鏈路測試開始前提供執行測試所需的主機軟件。這一過程不僅耗時長、效率低,而且在出現問題時調試難度大。

為了進一步強化測試過程,本文使用萊迪思AvantTM-X70 Versa板通過JESD204B IP鏈路,展示了與ADI 5G射頻前端ADRV9029評估板的互操作性。ADRV9029是專為5G應用設計的四通道寬帶射頻收發器。該設置展示了調制器生成OFDM模式和驗證無線鏈路的能力,無需依賴主機,顯著提高了測試的效率。

憑借集成了萊迪思FIR和iFFT IP核的OFDM調制器,我們現在可以更有效、更高效地驗證FPGA無線鏈路。

2、使用FIR和iFFT IP的OFDM調制器設計

2.1. 設計細節

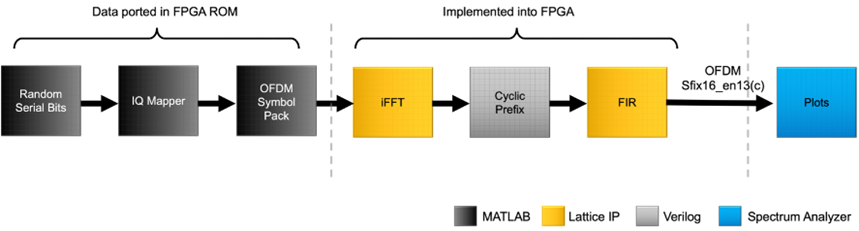

OFDM調制器設計利用了各種設計技術、工具和萊迪思IP核,包括MATLAB?、iFFT、FIR和手動編碼RTL。圖1顯示了OFDM調制器設計數據路徑的高層級框圖。采用FIR的OFDM調制器發送鏈彰顯了該調制方案在5G通信系統中的優勢。

圖1.調制器設計框圖

圖1中不同的顏色區分了不同的實現方法:

深灰色 :MATLAB生成的符號輸入FPGA ROM

黃色 :使用萊迪思IP核實現的模塊

淺灰色 :使用手動編碼的Verilog實現的模塊

藍色 :使用頻譜分析儀繪制頻譜圖以進行驗證

2.2. OFDM模式生成

OFDM模式發生器不斷重復并輸出相同的OFDM符號及其循環前綴。一組隨機調制符號在MATLAB中預先生成、處理并存儲在FPGA ROM中。ROM內容被讀入后續模塊,包括iFFT IP、循環前綴模塊和FIR IP,形成OFDM模式,并生成IQ數據饋送至射頻前端。下表顯示了設計中使用的OFDM模式系統參數。

表1. OFDM模式系統參數

2.3. 獨特功能和優勢

集成式設計:用戶可以直接在FPGA核中實現這一設計,無需借助外部設備。

成本和時間效率:這種設計減少了購買或借用外部設備以及建立復雜測試系統所需的成本和時間。

全面驗證:開發者可通過FPGA中的JESD204B IP核建立連接,并在開發套件上完成從功能仿真到硬件驗證的全流程測試。

2.4. 設計過程

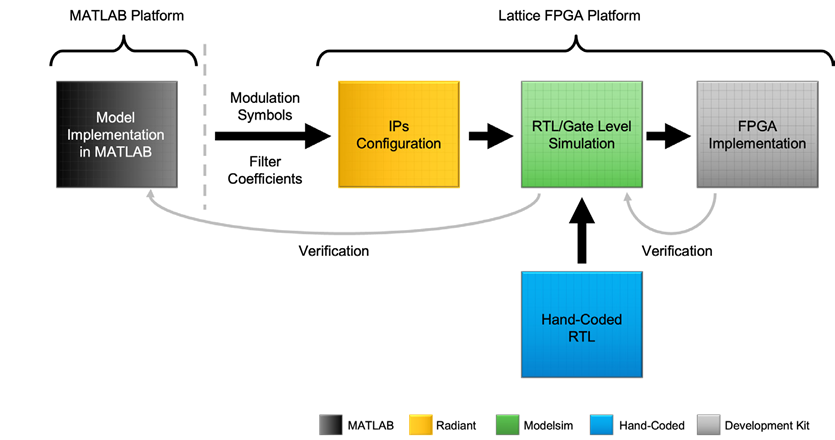

本節討論OFDM調制器的設計過程,從MATLAB模型的實現到萊迪思FPGA的實現。

2.4.1. 開發流程

基于萊迪思FPGA的OFDM調制器設計流程,始于在MATLAB中實現初始模型。此階段需根據需求參數完成調制器建模。并通過功率譜密度(PSD)圖驗證調制器輸出。生成的調制符號與sinc濾波器系數隨后被移植至萊迪思Avant? FPGA平臺。選擇Avant FPGA的關鍵在于其硬核DSP模塊與嵌入式存儲器的理想組合,能夠平衡處理能力與存儲容量。這些組件被集成至ROM IP核與FIR IP核中,確保無縫數據處理。此外,其他關鍵FPGA IP(如iFFT模塊)需根據調制符號生成時所用的FFT點數進行配置。

隨后,這些IP核將與手寫RTL模塊(包括循環前綴模塊)整合,構建完整設計。為確保設計的功能正確,需在QuestaSim?萊迪思版中進行RTL級仿真,并將仿真結果與MATLAB仿真數據細致比對以驗證其準確性。

最終階段需將設計部署至萊迪思FPGA開發套件。在此環節,硬件輸出結果需與RTL仿真數據嚴格比對。若驗證過程中發現偏差,需啟動全面調試并回溯前期階段實施修正,從而確保OFDM調制器設計達到穩健可靠的目標(參見圖2)。

圖2. 調制器設計開發流程

2.4.2. FPGA設計模塊

本節將討論FPGA中用于實現OFDM調制器的模塊。

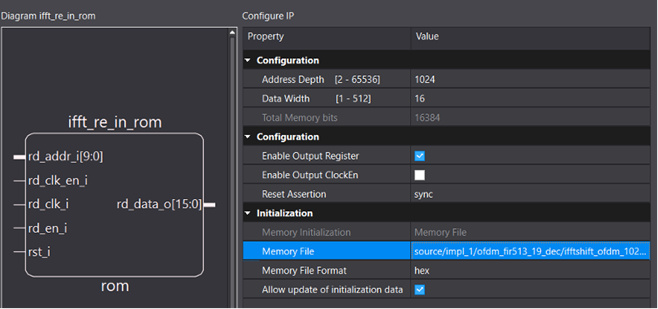

2.4.2.1. ROM

MATLAB生成的OFDM調制符號在轉換為定點格式之前被分成實部和虛部。然后將這些定點值轉換為十六進制(HEX)格式,并存儲在FPGA ROM中。在用戶模式下,ROM內容被輸入IFFT IP。圖3顯示了本設計中使用的萊迪思ROM IP配置示例。

圖3. 用于存儲調制符號實部的ROM IP配置

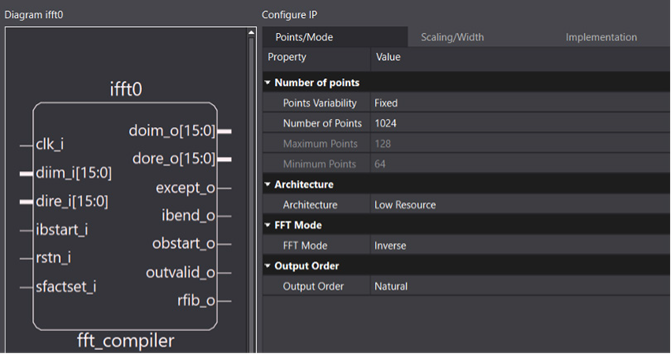

2.4.2.2. IFFT

在使用OFDM作為多載波調制技術的發射機中,OFDM符號的構建過程如下:首先在頻域將輸入位映射到64QAM調制符號的I路和Q路分量上,隨后根據OFDM符號中子載波的數量,將這些調制符號按特定長度(即iFFT點數)進行排序。通過這種映射和排序操作,即可構建出OFDM符號的頻域分量。為了傳輸這些信號,必須將其轉換到時域進行表示。這一轉換過程是通過快速傅里葉逆變換(iFFT)來實現的。

在該調制器設計中,每個64QAM符號被映射到一個頻率子載波,并使用萊迪思FFT Compiler IP在逆模式下轉換到時域。圖4顯示了本設計中使用的萊迪思FFT Compiler IP的配置示例。

圖4. 逆模式FFT Compiler的配置IP

2.4.3. 循環前綴

循環前綴是提高數據傳輸可靠性和效率的基本要素。在本設計中,OFDM符號的最后64個采樣在同一符號的開始處重復。這種有助于減少信號傳輸過程中的符號間干擾(ISI)。iFFT的輸出進入手寫編碼的循環前綴塊。

2.4.4. FIR Compiler IP

數據通路中的最后一個模塊是濾波器。該濾波器作用于時域OFDM符號,旨在抑制子帶信號的帶外輻射,同時保持OFDM符號的復域正交特性。為實現這一目標,FIR濾波器需滿足以下標準:

?在子帶內子載波上保持通帶平坦性

?陡峭的過渡帶設計以最小化保護帶需求?

具備充分的阻帶衰減性能

具有矩形頻率響應(即sinc脈沖響應)的濾波器可滿足上述標準。為實現因果性,需通過加窗方式實現該低通濾波器——具體而言,窗函數會對脈沖響應進行有效截斷,并在其兩端提供平滑過渡至零的衰減特性。

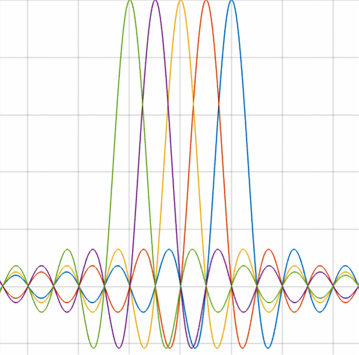

圖5顯示了頻域中5個相鄰子載波的示例圖,幅度歸一化為1,頻率間隔為1。所示的子載波具有正交性。每個子載波在頻域中表示為sinc函數。

圖5. 相鄰和正交子載波示例圖

在采用FIR濾波器的OFDM系統中,子帶OFDM信號會通過設計好的FIR濾波器進行處理。由于濾波器的通帶與信號帶寬相匹配,只有靠近頻帶邊緣的少量子載波會受到顯著影響。一個關鍵設計要點是,允許濾波器長度超過OFDM的循環前綴長度。通過采用加窗技術(結合軟截斷)的FIR濾波器設計,產生的符號間干擾被降至最低水平。

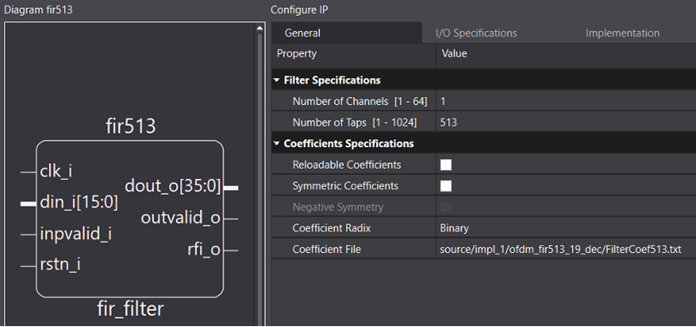

本設計中,首先使用MATLAB生成具有513個抽頭系數的sinc函數,隨后將這些參數導入FIR Compiler IP核。圖6展示了本設計采用的萊迪思FIR Compiler IP核配置示例。

圖6. FIR COMPILER IP配置

3、實現

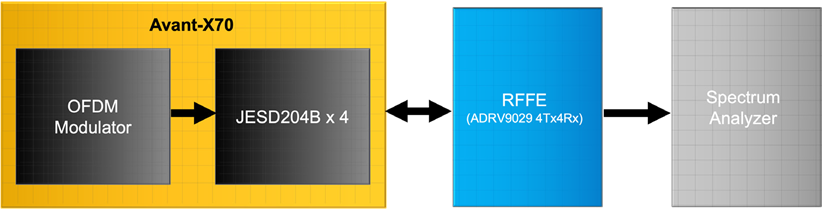

OFDM調制器設計是使用Avant-X70 Versa板在Avant-X70器件中實現。OFDM調制器與JESD204B鏈路層和物理層連接,向射頻前端ADRV9029發送數據。總共有4個JESD204B通道,每個通道的速度最高可達6.144Gbps。OFDM調制器和JESD204B IP在ADRV9029評估板上生成的153.6 MHz時鐘上運行,見圖 7。

圖7. 互操作性測試設置框圖:AVANT JESD204B和ADRV9029

3.1. 使用的軟件和硬件

本設計使用的軟件和硬件如下:

軟件:

萊迪思Radiant?軟件

tinySA?-App

MATLAB

硬件:

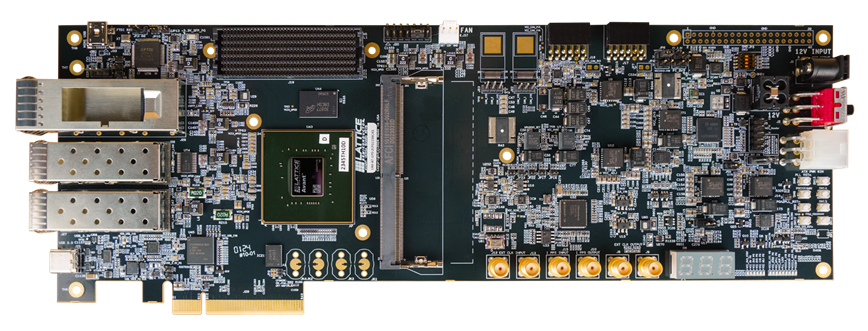

萊迪思Avant-X70(LAV-AT-X70-2LFG1156C)

萊迪思Avant-X70 Versa開發板

ADRV9029評估板

tinySA Ultra頻譜分析儀

圖8. AVANT-X70 VERSA開發板正面

3.2. 設計驗證

Avant-X70 Versa板與ADRV9029評估板通過JESD204B連接,通過硬件上的互操作性測試,對該設計進行了驗證。這一全面的驗證過程確保了設計實現的穩健性和可靠性。以下章節介紹了所使用的測試方法。

3.2.1. 互操作測試

Avant-X70 Versa開發板通過板上的FMC連接到ADRV9029評估板。

使用SMA線將ADRV9029輸出的射頻信號連接到頻譜分析儀,以采集PSD圖。

將該圖的帶寬與理論值進行比較,以確保正確實現。

4、結果和討論

4.1. AVANT-X70 VERSA開發板硬件測試

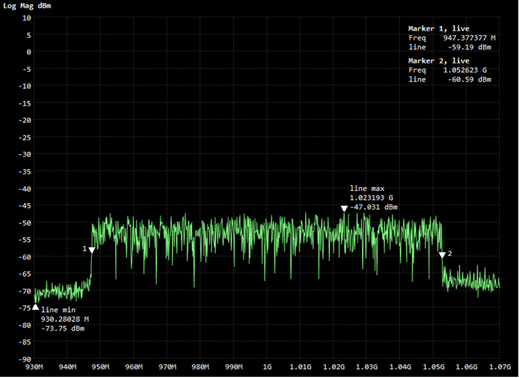

ADRV9029評估板輸出的射頻信號連接到頻譜分析儀,以采集PSD圖。PSD 的帶寬使用標記進行測量。圖9顯示了其中一個射頻信號輸出的PSD圖。

圖9. 頻譜分析儀上的PSD頻譜圖

從硬件測試結果中得出的主要結論如下:

PSD圖呈矩形

測得的帶寬 = 1052MHz - 947MHz = 105MHz

4.2. MATLAB仿真

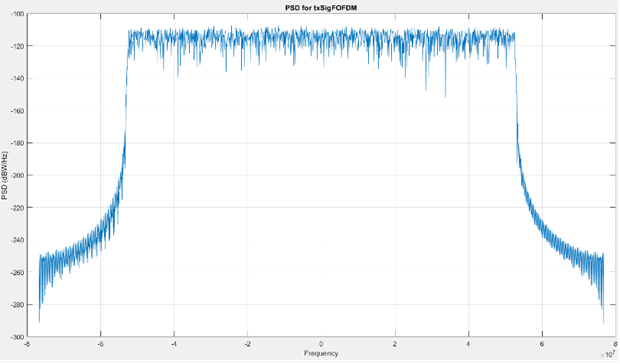

MATLAB模型輸出的OFDM調制器PSD圖與頻譜分析儀捕獲的PSD頻譜進行了比較。結果表明,MATLAB模型和硬件測試結果的PSD圖的形狀和帶寬都相匹配。

圖10. MATLAB模型輸出的OFDM PSD圖

4.3. 對結果的分析和解釋

在表1所述的OFDM模式系統參數下,頻譜分析儀捕捉到的PSD頻譜帶寬的預期理論計算如下:

OFDM帶寬= 數據子載波數 x 子載波間距 x 過采樣

= 700 X 15K x 10

= 105 MHz

PSD頻譜的預期帶寬為105 MHz,與MATLAB仿真和頻譜分析儀繪圖得出的帶寬值相符。

5、結論

5.1. 研究及結果概述

本文提出了一種基于萊迪思FFT Compiler IP核、FIR Filter IP核與手動編寫RTL代碼協同設計的OFDM調制器實現方案。Avant-X70 Versa開發板及ADRV9029評估板通過JESD204B接口進行互操作性測試,實測結果表明該設計具有高可靠性與穩定性?。此外理論值和頻譜分析儀采集的PSD頻譜帶寬結果相吻合,有效驗證了設計的功能完整性?。

5.2. 未來研究建議

今后的研究可側重于以下領域:

OFDM解調器的開發:解調器將完成環回數據路徑,在此可恢復接收到的OFDM符號,并與發送的符號進行核對。

6

本文使用的縮略語

評論