臺積電2nm N2工藝節點今年投產 A16和N2P明年上市

臺積電在其 2025 年北美技術研討會上透露,該公司有望在今年下半年開始大批量生產 N2(2nm 級)芯片,這是其首個依賴于全環繞柵極 (GAA) 納米片晶體管的生產技術。

本文引用地址:http://www.j9360.com/article/202504/469819.htm這個新節點將支持明年推出的眾多產品,包括 AMD 用于數據中心的下一代 EPYC“Venice”CPU,以及各種面向客戶端的處理器,例如用于智能手機、平板電腦和個人電腦的 Apple 2025 芯片。得益于 GAAFET 和增強的功率傳輸,新的 2nm 節點將在更高的性能和晶體管密度中實現切實的節能。此外,后續工藝技術 A16 和 N2P 有望于明年投產。

N2:準備在 2025 年下半年量產

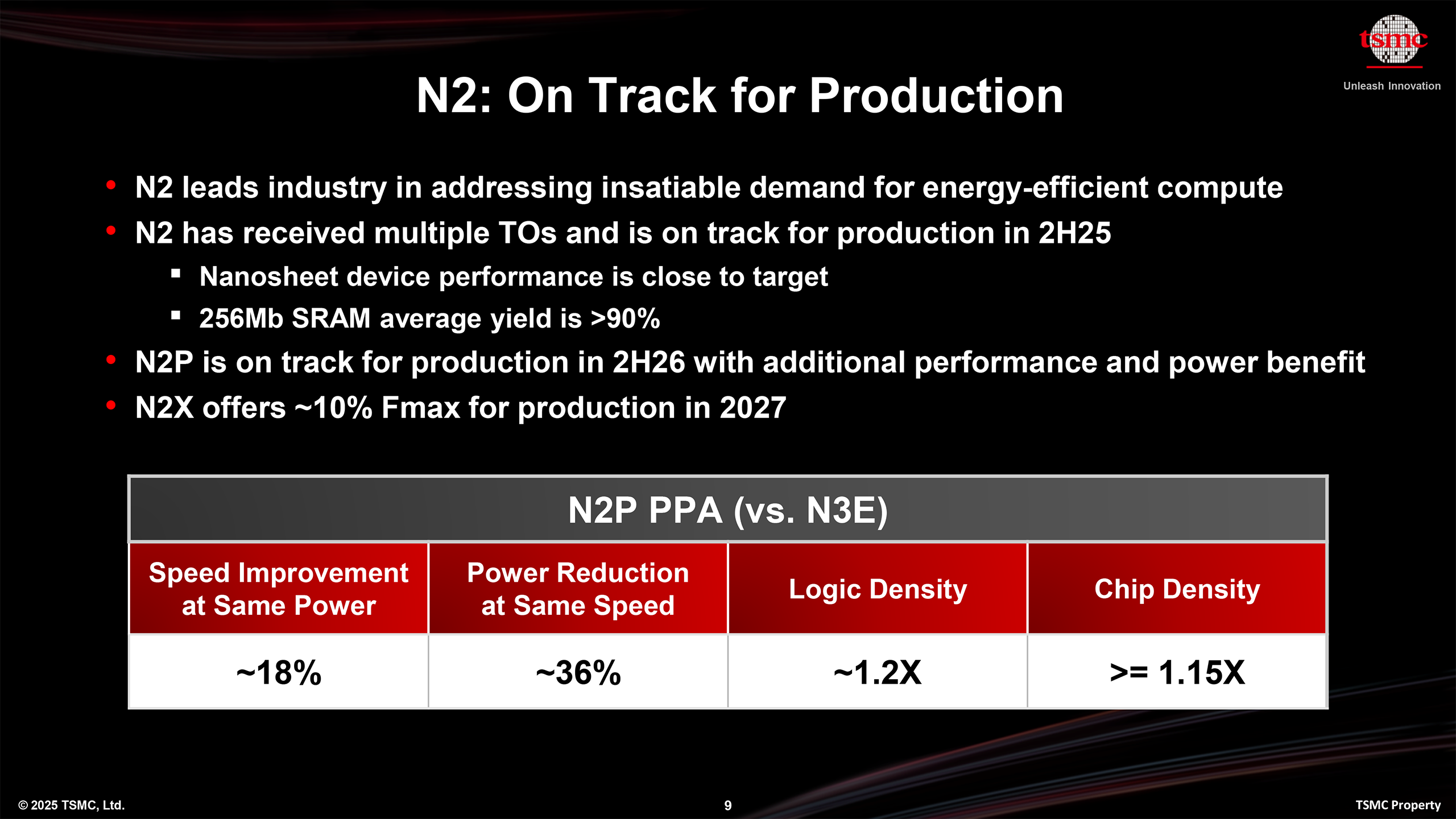

N2 是該公司的全新工藝技術,將實現臺積電所謂的“全節點改進”,其中包括與 N3E 相比,性能提高 10% 至 15%,功耗降低 25% 至 30%,晶體管密度增加 15%。臺積電表示,N2 的晶體管性能接近目標,256Mb SRAM 模塊的平均良率超過 90%,這表明隨著 N2 走向量產,工藝成熟度很高。

(圖片來源:臺積電)

如上所述,N2 將是臺積電第一個使用 GAA 納米片晶體管的節點,當柵極 360 度環繞通道時,該晶體管有望提高性能并降低泄漏——在 N2 的情況下,通道的形狀為多個水平納米片。這種結構允許最大限度地對通道進行靜電控制,從而在不影響性能或功率的情況下最小化晶體管尺寸,從而實現更高的晶體管密度。

此外,N2 工藝將超高性能金屬絕緣體金屬 (SHPMIM) 電容器集成到晶體管的輸電電路中,以增強電源穩定性和性能。與該公司之前的超高密度金屬-絕緣體-金屬 (SHDMIM) 設計相比,這些新型電容器的電容密度增加了一倍以上,并且與上一代產品相比,薄層電阻 (Rs) 和通孔電阻 (Rc) 降低了 50%,這應該會對性能和功耗產生切實影響。

宣傳 TSMC 新工藝技術的 PPA 改進

| Tom 的硬件 | N2 與 N3E | N2P 與 N3E | N2P 與 N2 | A16 與 N2P | N2X 與 N2P |

| 權力 | -25% ~ -30% | -36% | -5% ~ -10% | -15% ~ -20% | 降低 |

| 性能 | 10% - 15% | 18% | 5% - 10% | 8% - 10% | 10% |

| 密度* | 1.15 倍 | 1.15 倍 | ? | 1.07 倍 - 1.10 倍 | ? |

| 晶體管 | GAA | GAA | GAA | GAA | GAA |

| 電力輸送 | 正面帶 SHPMIM | 正面帶 SHPMIM | 正面帶 SHPMIM | 戰略風險 | 正面帶 SHPMIM (?) |

| HVM 系列 | 2025 年下半年 | 2026 年下半年 | 2026 年下半年 | 2026 年下半年 | 2027 |

*TSMC 公布的芯片密度反映了由 50% 邏輯、30% SRAM 和 20% 模擬組成的“混合”芯片密度。

**在同一區域。

以相同的速度。

該制造工藝有望在今年下半年進入量產,并將在明年推出眾多產品,包括 AMD 用于數據中心的下一代 EPYC“Venice”CPU,以及各種面向客戶端的處理器,例如用于智能手機、平板電腦和個人電腦的 Apple 2025 片上系統。

評論