展望2nm工藝的可持續(xù)性

隨著半導體制造復雜性的不斷增加,相關的排放量正在以驚人的速度增長。TechInsights Manufacturing Carbon Module 數據顯示,位于俄勒岡州的下一代 2nm 晶圓廠將生產 ~30 萬 MtCO2e 每年消耗超過 400 GWh 的電力。鑒于對電力和范圍 2 排放的依賴,晶圓廠選址也起著重要作用,位于臺灣的同等晶圓廠每年產生的排放量幾乎是其三倍。

本文引用地址:http://www.j9360.com/article/202503/468800.htm有勝利。具有高晶體管密度的精細工藝可以大大減少每個晶體管的輻射。半導體制造的碳中和是可能的,但正如我們將要展示的那樣,這需要齊心協力,并對可再生能源基礎設施進行大量投資。

通往 2nm 之路

英特爾、三星和臺積電都有望在未來 12-18 個月內發(fā)布下一代 logic 工藝。TechInsights 最近提出了一個技術展望,預計實施方面存在重大差異。

臺積電在 IEDM 2024 上詳細介紹了其 2nm 工藝。預計將于 2025 年下半年在臺灣開始量產。英特爾的等效工藝稱為“18A”,也計劃在同一時間范圍內生產,第一個使用該工藝的產品已經確定——英特爾的下一代 Panther Lake CPU。三星于 2023 年發(fā)布了業(yè)界首個全能門 (GAA) 工藝,然后在去年發(fā)布了量產部件(三星 Galaxy Watch7 的 W1000 處理器)。三星目前計劃等到 2026 年發(fā)布其 2nm 工藝。

臺積電的工藝將成為最密集的,而英特爾則率先推出反向供電 (BSPD) 網絡,他們稱之為“Power Via”,從而突破極限。三星已經擁有 3nm 的 GAA 經驗;如果它的產率足夠,理論上可以在將該工藝擴展到 2nm 時提供一些優(yōu)勢。這個下一代節(jié)點的獨特工藝流程,加上晶圓廠的選址和布置,將影響這些先進工藝對環(huán)境的影響。

范圍 2 排放和芯片良率的巨大影響

鑒于先進工藝的復雜性和功耗不斷增加,兩個因素對于減少排放至關重要 - 本地電網碳強度和產量。

對于此處的計算,我們將假設基于位置的電力(即基于晶圓廠位置的電網碳強度)。

從經濟學的角度來看,芯片良率至關重要;較低的良率意味著每個晶圓的合格芯片較少,從而增加了生產每個工作芯片的成本。盡管發(fā)布了業(yè)界首個 GAA 工藝,但三星的 SF3E 和 SF3 僅在相對小批量的市場中出現,并且使用小芯片尺寸。三星 Galaxy S25 系列沒有配備三星生產的新 Exynos 處理器這一事實引發(fā)了人們對 SF3 工藝良率是否足夠高以應對該應用的處理器尺寸和體積的問題。雖然低良率意味著每個芯片的成本更高,但碳排放也是如此。

從 TechInsights Manufacturing Carbon Module 獲取數據,我們來分析一些具體的例子。由于晶圓廠在不同的時間上線,具有不同的吞吐量,并且具有不同的供應鏈,因此很難進行同類比較。因此,鑒于 2nm 工藝需要幾年時間才能完全達到峰值產能,讓我們展望 2028 年;此時,3nm 和 2nm 都將是大批量運行的成熟工藝。

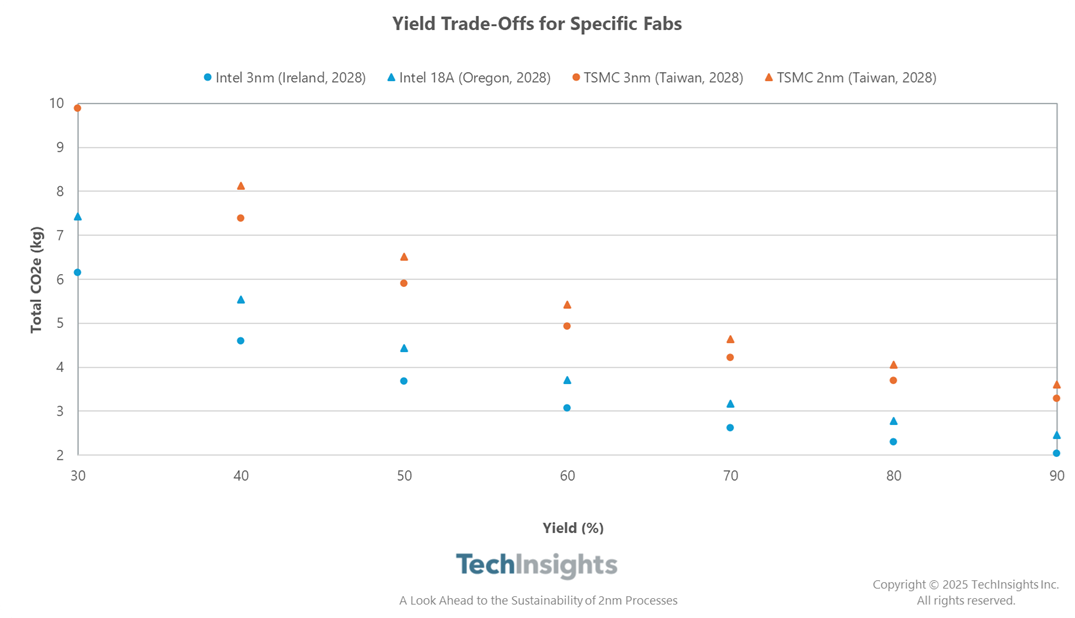

圖 1 比較了電網碳強度的兩種相反的極端情景,以英特爾和臺積電的晶圓廠為例,它們應該都在今年投入生產,并在 2028 年之前全面投產。

特定Fabs.png的收益權衡

特定Fabs.png的收益權衡

圖 1 比較具有不同本地電網碳強度的先進邏輯工藝。來源:TechInsights Manufacturing Carbon Module,2025 年

英特爾具有固有的電力優(yōu)勢,因為其 3nm 和 18A 工藝將在愛爾蘭和美國俄勒岡州相對低碳的電網中制造。

臺積電至少在最初將遭受臺灣可再生能源挑戰(zhàn),正如去年在深入的 TechInsights 分析中所討論的那樣。雖然 2nm 最終可能會在亞利桑那州臺積電生產,但可能需要 2030 年才能實現。到 2028 年,臺灣電網碳強度仍有望達到愛爾蘭或俄勒岡州的 2 倍以上。

與此同時,如果歷史是一個很好的指標,預計臺積電將有非常好的收益率,而對英特爾近期收益率的信心較低。正如 TechInsights 2nm 技術展望中所討論的那樣,一些消息來源表明英特爾的 18A 良率低至 10%。在 TechInsights,我們認為這不太可能,而且當芯片制造商開始量產時,它的產量肯定會顯著提高。盡管如此,英特爾與生俱來的電網優(yōu)勢意味著,即使英特爾的 18A 在其俄勒岡州工廠的產量僅為 60%,這仍然會產生與臺灣臺積電 2nm 工藝相似的排放,即 90%。換句話說,如果兩個工藝的產量均為 90%,那么臺積電 2nm Taiwan 工藝的排放量將增加 47%。

哪種下一代制造工藝最可持續(xù)?

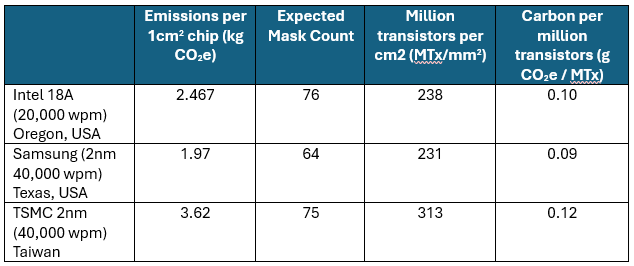

三星呢?韓國的電網碳強度略好于臺灣,但仍是俄勒岡州的兩倍多。然而,三星正在德克薩斯州泰勒建造一座先進的工廠,到 2026 年底可以生產 2nm。因此,現在讓我們切換到“2028 年最佳情況”,假設收益率為 90%。誰是贏家?表 1 顯示了一些重要的權衡。

表 1.2028 年代工廠生產 2nm 芯片的最佳情況。來源:TechInsights 的制造碳模塊,2025 年。

在這種情況下,三星在每芯片的基礎上獲勝,因為德克薩斯州的電網碳強度較低,而三星工藝的掩模數量較少。

如果我們以按晶體管縮放的方式看待事物,就會發(fā)生一個有趣的平衡。

TechInsights 對所有 2nm 等效工藝進行了晶體管邏輯密度計算,并認為它們如下:高密度邏輯單元晶體管密度為 313 MTx/mm2用于臺積電,238 MTx/mm2適用于 Intel,以及 231 Mtx/mm2對于三星。由此,我們還可以計算出 CO2e/MTx 的數字。在這種情況下,三星仍然獲勝。然而,情況要接近得多,由于晶體管密度高于三星工藝,臺積電更具競爭力。

這些結果仍應被視為初步的預期;所有過程都仍然存在問題。在撰寫本文時,盡管臺積電臺灣工藝的排放量最高,但它似乎確實是最有可能按計劃進行的過程。據報道,三星的德克薩斯州項目與英特爾的項目一樣,產量較低。假設亞利桑那州的臺積電 2nm 工藝在本世紀末加速發(fā)展。在這種情況下,臺積電也將受益于美國較低的網格強度,而這一工藝,再加上其增加的晶體管密度,將成為巨大的贏家。

2nm 實現碳中和需要什么?

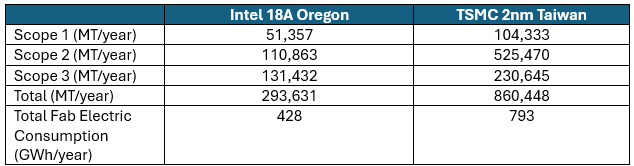

作為最后一個思想實驗 - 如何使 2nm 等效晶圓廠完全碳中和?讓我們回到 2028 年俄勒岡州的 Intel 18A 和 TSMC 2nm 的初步例子。表 2 細分了每個晶圓廠一年的排放量。

表 2.按范圍劃分的晶圓廠每年碳排放總量。來源:TechInsights 的制造碳模塊,2025 年。

在臺灣的例子中,范圍 2 排放占主導地位;然而,Intel 發(fā)生了一些奇怪的事情。盡管具有與 TSMC 工藝相似數量的掩模,但涉及 EUV 光刻的掩模要少得多。(我們估計英特爾芯片有 17 個掩碼,而臺積電有 24 個掩碼。BSPD 的實現允許在 Mx 層中實現寬松的間距,并減少多重圖形化)。這意味著范圍 2 的貢獻要低得多,盡管仍占總數的 38%。

范圍 2,即與電力消耗相關的間接排放,是指安裝可再生能源(如太陽能)可能會直接影響排放的地方。這將抵消英特爾晶圓廠每年使用的 428 GWh 總量多少?

假設這家英特爾工廠所在的俄勒岡州地區(qū)的太陽能發(fā)電容量系數為 20%,那么 1 MW 的太陽能光伏裝機容量每年將產生 1.752 GWh 的發(fā)電量。因此,需要一個 244 MW 的太陽能光伏裝置來抵消該工廠的電力消耗。就所需的土地面積而言,這相當于大約 12.5 公里2數組。臺灣的臺積電的太陽能容量系數較低,鑒于耗電量較高,與俄勒岡州的英特爾相比,總共需要大約三倍的裝機容量。

當然,范圍 2 只占故事的 38%。雖然范圍 1 排放量已經相對較低(我們估計該晶圓廠的氣體減排量為 98%),但剩余的 2% 將極具挑戰(zhàn)性,甚至可能無法以今天的技術減排。因此,碳中和的唯一途徑可能是使用碳抵消。范圍 3 也很復雜,需要在整個供應鏈中保持一致。如果我們要對剩余的 18 萬 MtCO 嘗試抵消方法2,環(huán)境保護署 (EPA) 的數據顯示,這相當于近 200,000 英畝(~8,00 平方公里) 美國森林一年的封存碳價值)。在 TechInsights 對 Apple 尋求碳中和的分析中,我們討論了其實現碳中和的碳抵消方法,顯示抵消這些排放水平是可能的,但并不簡單。

這些問題不僅對晶圓廠的報告目的很重要,而且對整個供應鏈(即無晶圓廠半導體公司或產品制造商)也很重要。這將繼續(xù)推動整個半導體價值鏈合作,并在控制先進半導體制造排放方面取得有意義的進展。故事并沒有就此結束;正如最近的 TechInsights 分析中所討論的那樣,2nm 將使用額外的水和含 PFAS 的化學品。

(注:本文登于EEPW 202504期)

評論