一文看懂TSV技術

前言

本文引用地址:http://www.j9360.com/article/202311/453003.htm從HBM存儲器到3D NAND芯片,再到CoWoS,硬件市場上有許多芯片是用英文稱為TSV構建的,TSV是首字母縮寫,TSV(Through Silicon Via)中文為硅通孔技術。它是通過在芯片與芯片之間、晶圓和晶圓之間制作垂直導通;TSV技術通過銅、鎢、多晶硅等導電物質的填充,實現硅通孔的垂直電氣互聯,這項技術是目前唯一的垂直電互聯技術,是實現3D先進封裝的關鍵技術之一。在本文中,我們將告訴您它們是什么,它們如何工作以及它們的用途。

在2000年的第一個月,Santa Clara University的Sergey Savastiou教授在Solid State Technology期刊上發表了一篇名叫《Moore’s Law – the Z dimension》的文章。這篇文章最后一章的標題是Through-Silicon Vias,這是Through-Silicon Via這個名詞首次在世界上亮相。這篇文章發表的時間點似乎也預示著在新的千禧年里,TSV注定將迎來它不凡的表演。

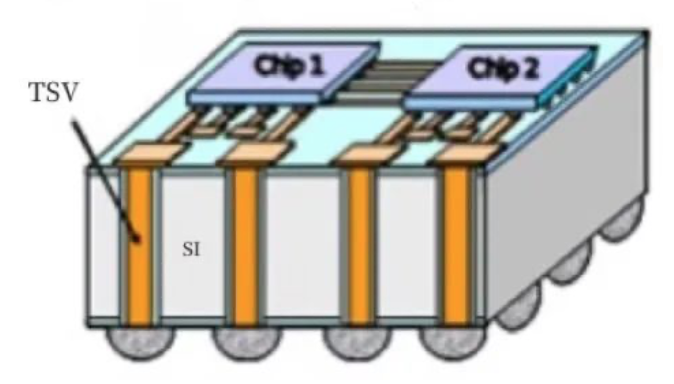

TSV示意圖

如果說Wire bonding(引線鍵合)和Flip-Chip(倒裝焊)的Bumping(凸點)提供了芯片對外部的電互連,RDL(再布線)提供了芯片內部水平方向的電互連,那么TSV則提供了硅片內部垂直方向的電互連。 作為唯一的垂直電互連技術,TSV是半導體先進封裝最核心的技術之一。

90年代中期,半導體行業發生一件大事: IBM用銅電鍍大馬士革工藝全面替代的濺射鋁作為集成電路中晶體管互連。這樣電鍍銅在半導體行業便開始成為標準工藝,這讓電鍍銅用于TSV的微孔金屬化填充更加順理成章。

至此, 現代TSV的兩項核心技術:深硅刻蝕和電鍍都出現了。

TSV不僅賦予了芯片縱向維度的集成能力,而且它具有最短的電傳輸路徑以及優異的抗干擾性能。隨著摩爾定律慢慢走到盡頭,半導體器件的微型化也越來越依賴于集成TSV的先進封裝。TSV對于像CMOS Image Sensor(CIS,CMOS圖像傳感器),High Bandwidth Memory(HBM)以及Silicon interposer(硅轉接板)都極其重要。因為存在感光面的緣故,CIS芯片的電信號必須從背部引出,TSV因此成為其必不可少的電互連結構。

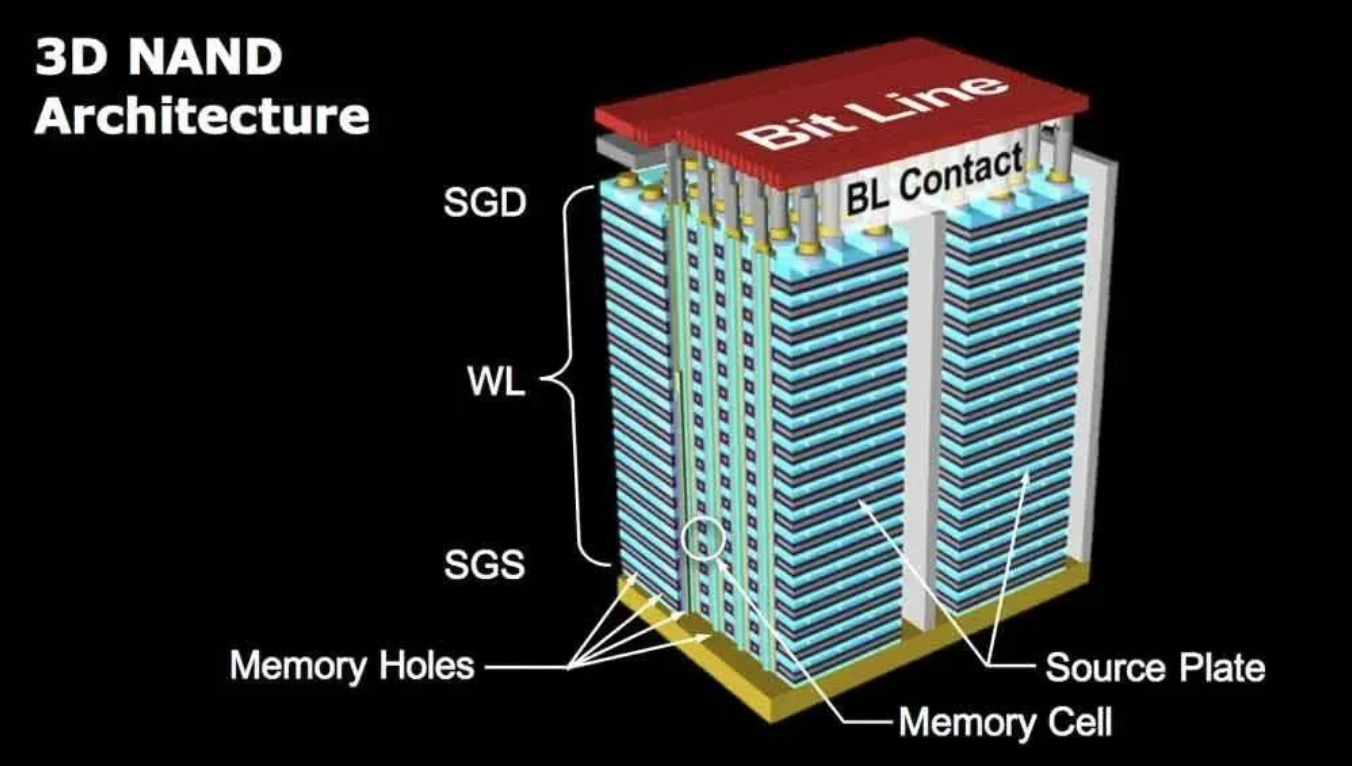

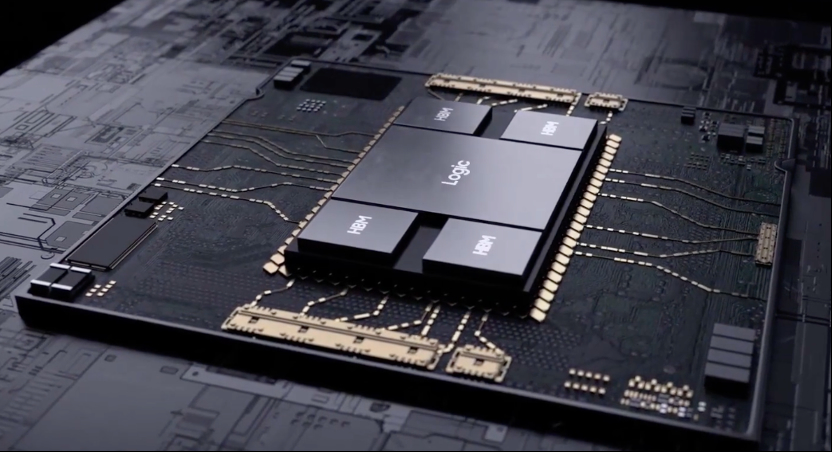

HBM是基于多層堆疊的存儲芯片,如今HBM已經可以實現12層的堆疊,16層以上更多層的堆疊相信在不久的將來也會實現,當然這一切都離不開TSV的互連。而Silicon interposer可以將多種芯片,像CPU、memory、ASIC等集成到一個封裝模塊的關鍵組件,它的垂直互連同樣需要TSV。事實上,法國的Yole development咨詢公司曾做過一項研究發現TSV幾乎可以應用于任何芯片的封裝以及任何類型的先進封裝,包括LED、MEMS等。

正是因為TSV的重要性,各大Foundry和OSTA公司也不斷投入TSV技術的研發。這階段的研發重點是如何保證電鍍沉積主要發生在TSV孔內而不是硅片表面。如果不采取任何措施,電鍍時硅表面金屬沉積的速度會遠快于TSV孔內。這個問題目前的解決方法是在電鍍液中添加抑制劑和加速劑,分別抑制硅片表面的金屬沉積并加速TSV孔內的沉積。為了獲得完美的填充效果和足夠高的良率,各大Foundry和OSTA公司都做了大量研究以獲得最佳的電鍍的參數,例如電流,溫度,硅片的與電極的相對位置,添加劑的濃度等。各大半導體設備公司也開始針對TSV的電鍍推出專用的半導體設備。

在硬件世界中,經常用與速度有關的術語來談論它,即是否是內存的帶寬,處理器的時鐘周期,處理器每秒執行某種類型的計算的次數等等,但是我們很少問自己這些芯片如何相互通信以及這是否重要。

在本文中,我們將討論一種稱為TSV的技術,該技術可用于相互通信的芯片。

什么是硅或TSV通路?

如果我們看大多數主板,可以看到兩件事:第一,芯片之間的大多數連接都是水平的,這意味著板上發送芯片間信號的路徑是水平通信的。

PCB

然后是CPU的情況,這些CPU放置在我們稱為插座的插入器的頂部,并且處理器在這些插入器上垂直連接。

Socket CPU

但是通常,在99%的時間中,我們觀察到通常沒有相互垂直連接的芯片,盡管事實上芯片和處理器的設計朝著這個方向發展,并且市場上已經有這種類型的示例。但是,如何使兩個或更多芯片垂直互連?

TSV

好吧,正是通過所謂的硅通道來完成的,硅通道垂直穿過組成堆棧的同一芯片的不同芯片或不同層,這就是為什么它們被稱為“通過”硅通道,因為它們實際上是通過的。

使用TSV的應用和優勢

TSV的應用之一是,它允許將由不同部分組成的復雜處理器分離在幾個不同的芯片上,并具有以下附加優點:垂直連接允許更多數量的連接,這有助于實現更大的帶寬,而無需額外的帶寬。很高的時鐘頻率會增加數據傳輸期間的功耗。

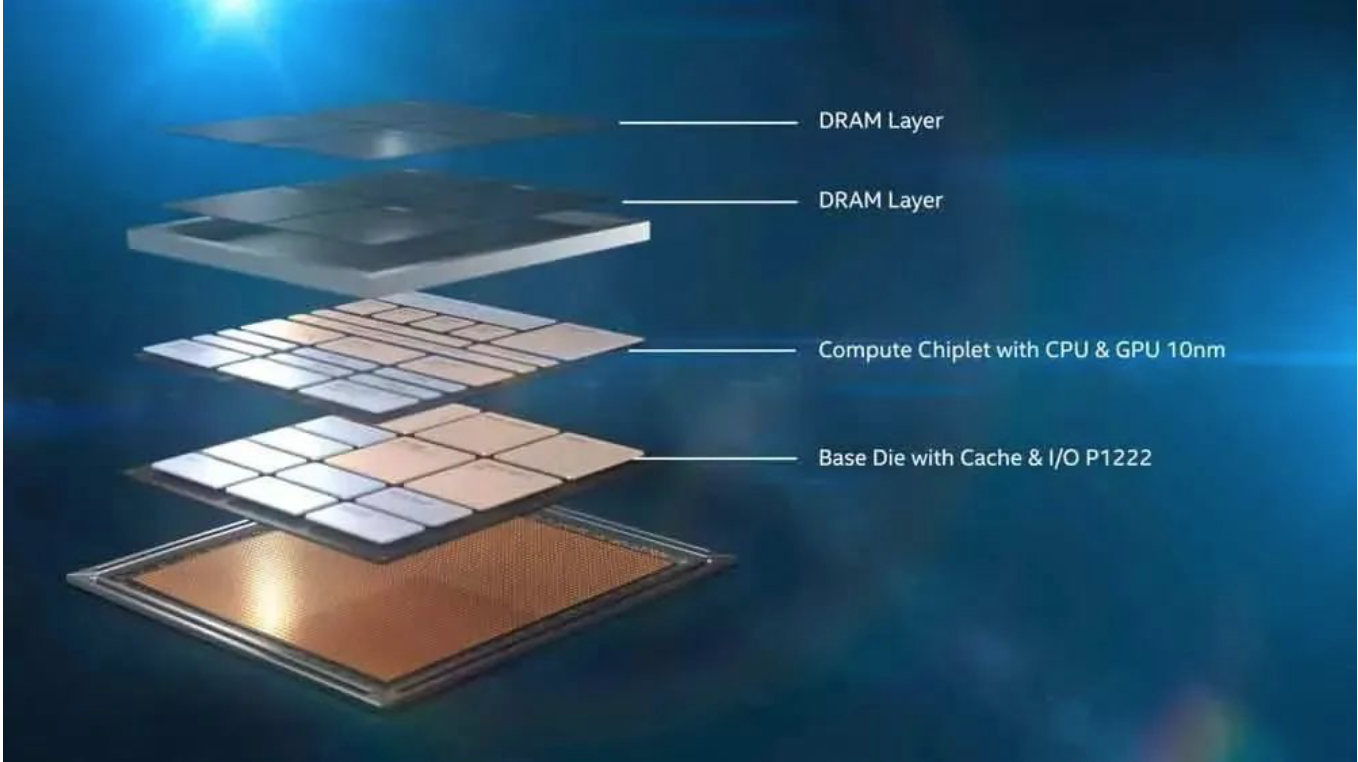

例如,在將來,我們將看到CPU和GPU的最后一級緩存將不在芯片上,它們具有相同的帶寬,但存儲容量卻是原來的幾倍,這將大大提高性能。我們也有使用FSV來通信Lakefield SoC的兩個部分的Intel Foveros示例,即帶有系統I/O所在的基本芯片的計算芯片。

Lakefield Foveros

將處理器劃分為不同部分的原因是,隨著芯片的變大,電路中錯誤的可能性越來越大,因此沒有故障的優質芯片的數量會增加。他們可以使用的更少,而那些做得好的人必須支付失敗者的費用;這意味著從理論上減小芯片的尺寸會降低總體成本,盡管稍后我們將看到情況并非完全如此。

HBM-vs-GDDR

第二個應用程序與占用的空間有關;能夠垂直堆疊多個芯片的事實大大減少了它們占用的面積,因為它們不會散布在板上,其中最著名的示例是將HBM內存用作某些圖形處理器的VRAM,但是我們還有其他示例,例如三星的V-NAND存儲器,將多個NAND閃存芯片彼此堆疊。

3D NAND

其他鮮為人知的選擇是邏輯和內存的組合,其中內存位于處理器的頂部,最著名的示例是寬I/O內存,這是幾年前出現在智能手機中的一種內存,包括SoC頂部的存儲器通過硅互連。

TSV這項并不為人熟知的技術,正在硬件的底層深深的影響著人類的生產生活方式。半個多世紀前的那個秋天,肖特基那個在硅片上打孔的想法最終將人類帶入了人工智能的時代。

來源:芯片半導體實驗室

評論