DDR5可望成為下一代主流存儲器接口?

存儲器頻寬與密度都比目前DDR4更高2倍的DDR5存儲器介面芯片來了,預計最快在2019年量產,為服務器的主存儲器帶來更高效能與功率管理…

本文引用地址:http://www.j9360.com/article/201709/364712.htm存儲器世代即將來到DDR5 (第五代雙倍數據率)的時代!

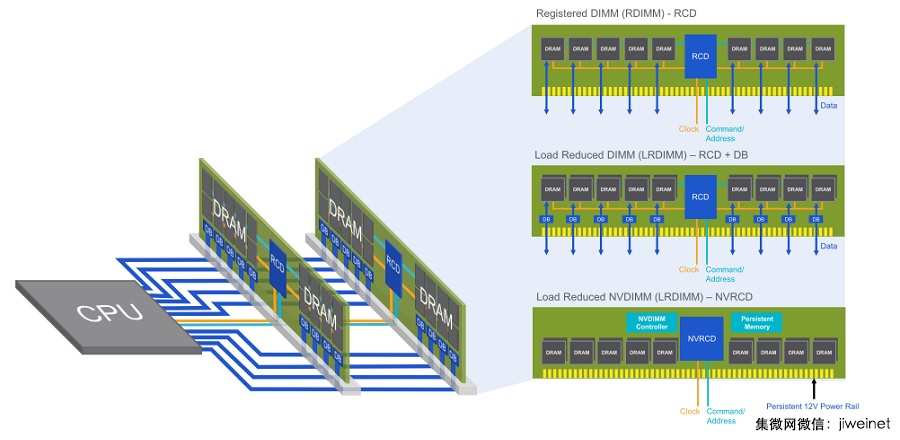

Rambus最近宣布在其實驗室中開發出DDR5的可用芯片——DDR5是動態隨機存取存儲器(DRAM)雙列直插式存儲器模組(DIMM)的下一代重要介面。預計從2019年開始,暫存時脈驅動器與數據緩沖器可望有助于為服務器倍增主存儲器的傳輸速率,而且也引發了對于未來運算的爭論。

美國聯合電子裝置工程委員會(JEDEC)標準組織計劃在明年6月之前宣布以DDR5規格作為下一代服務器的預設存儲器介面。然而,有些分析師指出,DDR5出現的時機,將會在持久型存儲器(即儲存級存儲器)、新式電腦架構與芯片堆疊等均陸續更新替代方案之際。

Rambus產品行銷副總裁Hemant Dhulla表示:“據我們所知,這是至今第一個在實驗室中開發出實際可行的DDR5 DIMM芯片組,預計可在2019年量產。我們希望率先使其上市,并協助我們的合作伙伴推出該技術。”

DDR5預計可支持高達6.4Gbits/s的數據率,傳輸頻寬最高達51.2 GBytes/s,分別較目前的DDR4支持的3.2Gbits數據率與25.6GBytes/s傳輸頻寬提高一倍。升級后的新版本將使64位元鏈路的運作壓從1.2V降低至1.1V,并使突發周期(BL)從8位元進展至16位元。此外,DDR5可還讓電壓穩壓器安裝于該記憶卡,而不必再加進主板中。

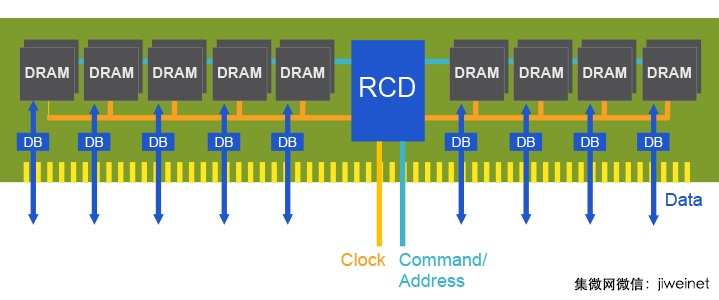

下一代服務器DIMM緩沖器芯片瞄準DDR5存儲器應用(來源:Rambus)

同時,CPU供應商預計將使其處理器的DDR通道數從12個擴增到16個通道,從而可能使主存儲器的容量從現有的64GB提高到128GB。

預計DDR5將最先出現在執行大型數據庫的高性能系統,或是諸如機器學習等具有龐大存儲器容量需求的應用中。Dhulla表示,雖然有些服務器可能會延遲達6個月才采用DDR5,“但這只不過是幾季的時間罷了,并不是好幾年……每個人都想要更大容量的存儲器。”

當今大約有90%的服務器都采用暫存或降低負載的DIMM——這些DIMM則采用暫存器時脈以及數據緩沖器。這些芯片通常由Rambus、IDT和Montage等公司以不到5美元的價格銷售。

替代型存儲器崛起

DDR5標準出現的時間,大約就是JEDEC為支持一系列DRAM與持久型存儲器組合的存儲器模組發布NVDIMM-p (非揮發性DIMM)介面之際。英特爾(Intel)表示將在明年推出采用其3D XPoint芯片的服務器DIMM;其他公司也預計將推出采用3D NAND的NVDIMM-p存儲器。

相較于傳統的DRAM模組,新版存儲器預計將在密度和延遲方面更具優勢。不過,預計其價格也將會更高,而DRAM可望維持原始速度的優勢。

DDR5介面芯片的存儲器頻寬與密度都比DDR4更高2倍(來源:Rambus)

市場研究公司WebFeet Research總裁Alan Niebel表示:“市場將會非常需要DDR5...但它仍然是DRAM,而且也很耗電。它推動了傳統的馮·諾伊曼(Von Neuman)系統進展,但我們仍然需要持續推出持久型存儲器替代方案,以及新的運算模式。”

事實上,Hewlett-Packard Enterprise (HPE)已經發布了一款采用Gen-Z存儲器介面的原型系統。Gen-Z是在今年8月才推出的全新存儲器架構。

WebFeet首席分析師Gil Russell表示:“許多人并不看好DDR5能成為下一代的存儲器介面。”

DRAM的制程技術微縮正趨近于其核心電容器的實體限制,這使得Russell等業界分析師預期這種存儲器設計將在未來的5至10年內終結。他強調,更高的錯誤率必須在芯片上建置糾錯程式碼的電路。

然而,存儲器領域“是一個真正進展緩慢的領域。”Russell說:“要讓DIMM獲得市場的認可,大概就得花一年的時間,而且大家總想要以盡可能最低的成本導入。”

同時,為了進一步提高速度與密度,AMD和Nvidia的高階繪圖處理器(GPU)已經改用高頻寬的存儲器芯片堆疊了。Rambus的Dhulla指出,芯片堆疊仍然是一種昂貴的途徑,僅限于用在高階的GPU、FPGA以及通訊ASIC。

Dhulla表示,“DDR5顯然是開啟大量機會的理想途徑。但目前業界較大的爭論焦點是在DDR5之后以及2023年以后將如何發展。因此,我們的實驗室也正著眼于多種替代方案。”

評論