采用兩級電路實現的地址變化探測器

靜態隨機存取存儲器(SRAM)由于其優越的性能(速度高、功耗低),被廣泛應用于作為高速緩存的最大量的揮發性存儲器。 近年來隨著便攜式數字電子產品的日益普及,SRAM速度高、功耗低的要求也越來越強烈,這亦成為SRAM未來發展的主要趨勢。

提高速度、降低功耗是SRAM設計的主要目標。提高其性能的關鍵是設計好單元和讀出靈敏放大器,此外在總體結構設計上也采取了許多措施改善SRAM的性能。本文提出一種新型地址變化探測電路來降低SRAM的維持功耗和提高工作速度,更提高了SRAM的抗噪聲、抗干擾能力。

1 傳統地址變化探測器電路

SRAM有異步和同步之分,它們的結構和速度各異。對于異步SRAM為了降低SRAM的維持功耗和提高工作速度,設計了一種自定時方式,增加了一個地址變化探測器。當地址變化出現時,電路自動檢測該地址總線上的任何變化。不需要任何外部的時序信號,可產生一個ATD信號,所有內部的時序操作(如啟動譯碼器和靈敏放大器等)都來自內部產生的翻轉信號,而不必等待同步時鐘信號控制,從而提高了工作速度。這一方法的優點是使SRAM的存取時間接近或等于它的周期時間。 另外,譯碼器受ATD信號控制,在維持狀態下使所有的字線都為低電平,這將消除維持狀態下的列電流,進一步降低芯片的功耗。

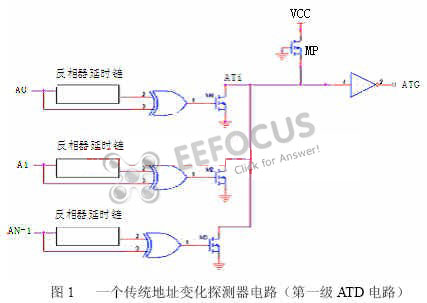

圖1為一個傳統地址變化探測器電路。A0到An-1任何一個端口輸入信號上的翻轉都會引起ATi下降到低電平并持續一個時間,由此產生的脈沖作為存儲器其余部分主要的時序參考。

傳統地址變化探測電路在提高速度和降低功耗的優點是顯而易見的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信號間的耦合而造成的噪聲電平,同時對速度的更高要求也使得存儲器的切換噪聲也相應增加。尤其當PAD上有外部干擾信號影響時,將會改變ATD的脈寬,從而導致SRAM的讀寫錯誤。

傳統地址變化探測電路在提高速度和降低功耗的優點是顯而易見的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信號間的耦合而造成的噪聲電平,同時對速度的更高要求也使得存儲器的切換噪聲也相應增加。尤其當PAD上有外部干擾信號影響時,將會改變ATD的脈寬,從而導致SRAM的讀寫錯誤。

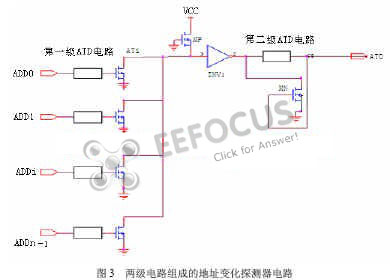

本文在傳統地址變化探測電路的基礎上,增加一級新型地址變化探測器電路,構成有兩級電路組成的地址變化探測器電路,來提高SRAM的抗噪性。

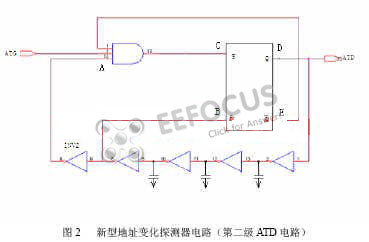

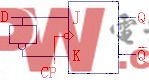

圖2為新型地址變化探測器電路

新型地址變化探測器電路(圖2)的工作原理如下:

1 ) 電路初始化

沒有任何地址變化時,由上拉管MP將ATi 置為高電平,由反相器INV1,ATG置為低電平;通過三輸入與門,C為低電平。

當C為低電平,B為高電平時,則由RS觸發器,D為低電平,E為高電平;由延時鏈和反相器INV2,A為高電平,B為低電平;A、B、C、D、E處的電位將保持穩定狀態。

當C為低電平,B為低電平時,若當RS觸發器原狀態D為低電平,E為高電平;由延時鏈和反相器INV2,A為高電平,B為低電平;A、B、C、D、E處的電位將保持穩定狀態。

當C為低電平,B為低電平時,若當RS觸發器原狀態D為高電平,E為低電平;由延時鏈和反相器INV2,A為低電平,B為高電平;由RS觸發器,E為高電平,D為低電平;再由由延時鏈和反相器INV2,A為高電平,B為低電平;A、B、C、D、E處的電位將保持穩定狀態。

因此,當電路初始化后,A和E被置為高電平,B、C和D(ATD)被置為低電平。

2) 當任一地址ADDi有變化時,第一級電路將ATi置為低電平。在第二級電路中,當任一ATi為低電平時,則ATG將為高電平,C也將為高電平。當C為高電平時,即將RS觸發器S端置為高電平,所以Q端為高電平,即D(ATD)為高電平。同時E為低電平,通過反饋環使C翻轉為低電平,此時B為初態低電平,因此觸發器保持狀態。當D點高電平經過延時反相器鏈將B置為高電平,D翻轉為低電平,從而產生一個完整的ATD信號。

3) 延時反相器鏈中反相器寬長比尺寸的調整將決定B點的瞬態電壓,這也是決定ATD信號脈寬的關鍵。

3 仿真結果

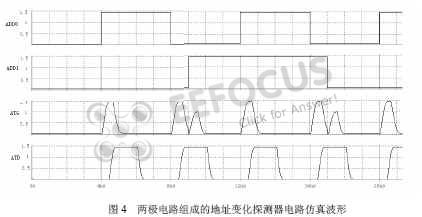

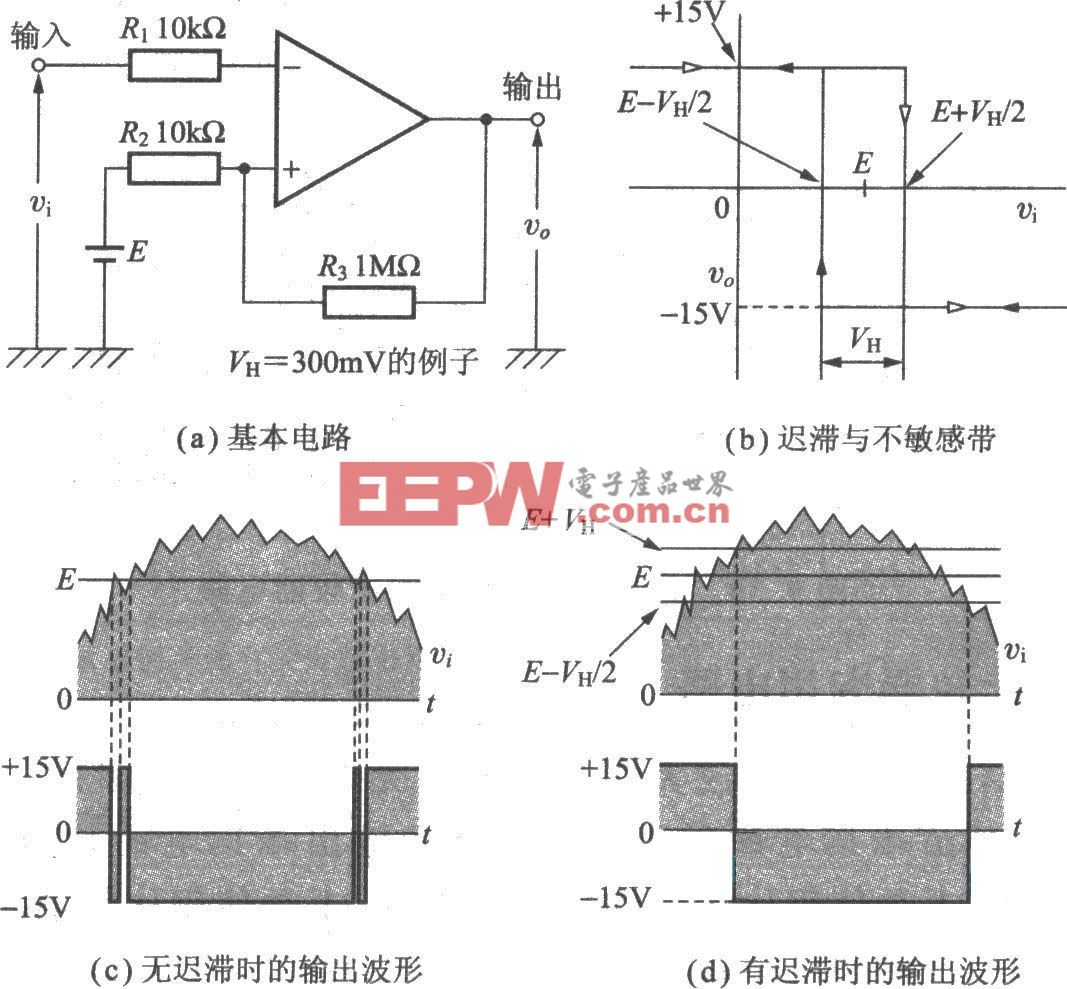

圖4是用HSPICE對采用兩級電路實現的地址變化探測器進行仿真的波形。由此波形圖可以看出,當地址端ADD0有地址信號輸入時,經過第一級ATD電路(傳統地址變化探測器電路),ATG將會產生需要的脈沖信號;而當地址端ADD1有不期望的干擾信號輸入時 ,經過第一級ATD電路(傳統地址變化探測器電路),ATG則會產生不需要的脈沖信號。然而經過第二級新型地址變化探測器電路,不期望的干擾信號被拒絕,輸出需要的ATD信號。

由ATG和ATD的波形可以看出,兩級電路實現的地址變化探測器雖然提高了抗干擾能力,但是,產生了一定的時間延遲。所以,本電路抗干擾能力的提高,導致了SRAM的存取速度降低。

4 結束語

地址變化探測器電路對于SRAM采用異步工作方式時非常重要,ATD信號是大多數時序信號的來源,并且還是關鍵路徑的一部分。ATD技術降低了SRAM的功耗同時提高了它的工作速度。在大容量、高密度、高速度的SRAM設計中,傳統地址變化探測器電路的抗噪聲、抗干擾能力不足。本文作者創新點是提出了含有兩級電路的地址變化探測器電路,雖然由于加入第二級的新型地址變化探測器電路降低了SRAM的速度,但是其大大提高了SRAM的抗噪聲、抗干擾能力。

評論