基于EDA的數據傳輸系統的HDB3編碼器

0 引言

本文引用地址:http://www.j9360.com/article/189854.htm數字基帶信號的傳輸是數字通信系統的重要組成部分。在數字通信中,有些場合可不經過載波調制和解調過程,而對基帶信號進行直接傳輸。采用AMI碼的信號交替反轉,有可能出現四連零現象,這不利于接收端的定時信號提取。而HDB3碼因其無直流成份、低頻成份少和連0個數最多不超過三個等特點,而對定時信號的恢復十分有利,并已成為CCITT協會推薦使用的基帶傳輸碼型之一。為此,本文利用VHDL語言對數據傳輸系統中的HDB3編碼器進行了設計。

1 HDB3碼的編碼規則

HDB3碼是AMI碼的改進型,稱為三階高密度雙極性碼,它克服了AMI碼的長連0串現象。

HDB3碼的編碼規則為先檢查消息代碼(二進制)的連0串,若沒有4個或4個以上連0串,則按照AMI碼的編碼規則對消息代碼進行編碼;若出現4個或4個以上連0串,則將每4個連0小段的第4個0變換成與前一非0符號(+1或-1)同極性的V符號,同時保證相鄰V符號的極性交替(即+1記為+V,-1記為-V);接著檢查相鄰V符號間非0符號的個數是否為偶數,若為偶,則將當前的V符號的前一非0符號后的第1個0變為+B或-B符號,且B的極性與前一非0符號的極性相反,并使后面的非0符號從V符號開始再交替變化。

2 HDB3編碼器的VHDL建模與程序設計

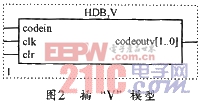

HDB3碼的VHDL建模思想是在消息代碼的基礎上,依據HDB3編碼規則進行插人“V”符號和“B”符號的操作,且用2位二進制代碼分別表示。最后完成單極性信號變成雙極性信號的轉換。其編碼模型如圖1所示。

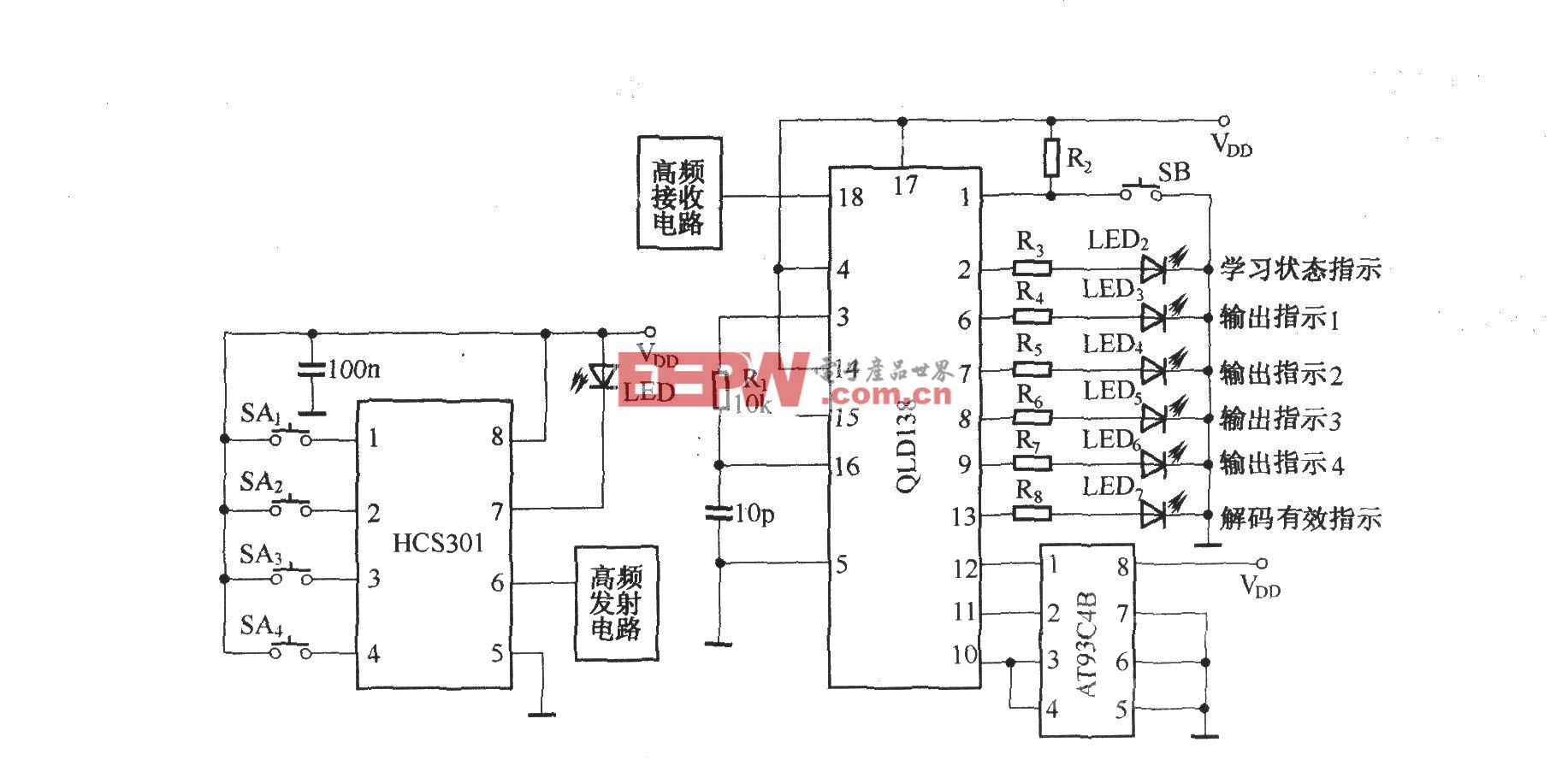

2.1 插“V”模塊的實現

插“V”模塊主要是對消息代碼里的四連0串的檢測,即當出現四個連0串的時候,把第四個“0”變換成符號“V”,用“11”標識。 “1”用“01”標識,“0”用“00”標識。其模型如圖2所示,實現的VHDL結構代碼如artv:

評論