基于EDA的數據傳輸系統的HDB3編碼器

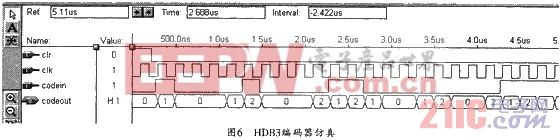

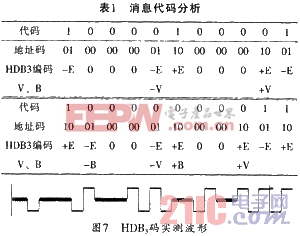

在此,以四連“0”的可能性通過如表1所列的多“0”消息代碼進行分析,并利用EDA工具對VHDL源程序進行編譯、適配、優化、邏輯綜合與仿真。仿真結果顯示其完全可以達到編碼要求。其仿真圖如圖6所示。而將HDB3編碼硬件描述下載到CPLD或FPGA目標芯片中,然后連接好CC4052進行實際應用測試(用示波器測得)的編碼波形如圖7所示。

4 結束語

將基于VHDL的HDB3編碼用在光纖通信系統中作為誤碼儀測試誤碼的HDB3轉換器,能滿足實際測試的需要。且運用基于VHDL的可編程芯片開發技術將相關的信號處理電路進行硬件描述,并用CPLD/FPGA技術實現數字通信系統,不僅可以實現多種數字邏輯功能,而且可大大提高工作效率,減少電路設計的時間和可能發生的錯誤,同時也可降低開發成本。

評論