基于TMS320C5402的語音信號壓縮存儲系統設計

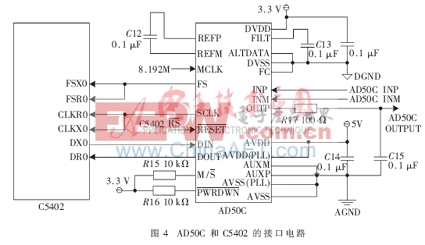

TLC320AD50C支持與TMS320C5402無縫對接,接口電路如圖4所示。將TLC320AD50C設置成主動工作模式,輸入主時鐘MCLK為8.192 MHz,采樣頻率選擇為8 kHz,內部PLL使能(控制寄存器4中的N=8)[2]。通過寄存器設置,將TMS320C5402的FSX、FSR、CLKR、CLKX配置為外部輸人,TLC320AD50C的SCLK配置為內部產生。數據接收/發送幀同步信號、移位時鐘信號均由TLC320AD50C產生,串行口的接收/發送過程受TLC320AD50C的控制。本文引用地址:http://www.j9360.com/article/166635.htm

3 系統軟件接口設計

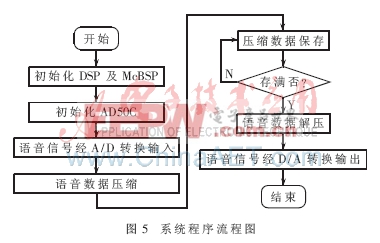

系統程序流程圖如圖5所示,軟件設計工作主要包括以下幾方面:

(1)TMS320VC5402串口的初始化。首先將DSP串口0復位,再對串口0的寄存器進行編程,使DSP串口工作在以下狀態:以SPI模式運行,每幀一相,每相一個字,每字16 bit,幀同步脈沖低電平有效,并且幀同步信號和移位時鐘信號由外部產生[3]。

(2)AD50C初始化。該初始化操作過程包括通過TMS320C5402的同步串口發送2串16 bit數字信息到AD50C。第一串為0000 0000 0000 0001B,最低有效位(bits0)為1,說明下一個要傳輸的數據字屬于次通信。第二個數據用來對AD50C的4個控制寄存器的某一個進行配置。15~11位為0,10~8位為所選寄存器地址值,7~0位為所選中寄存器的編程值。通過對4個可編程控制寄存器編程,使AD50C工作在以下狀態:選擇INP/INM為工作模擬輸入,15+1 bit ADC和15+1 bit DAC模式,不帶從機,采樣頻率為8 kHz,模擬信號輸入和輸出放大增益均為0 dB[4]。4個寄存器初始化需要4個主通信和次通信。

(3)壓擴算法的實現。TMS320C5402內部的緩沖串口(McBSPs)帶有硬件實現的μ律和A律壓縮解壓,用戶只需要在相應寄存器中進行設置就可以了,本系統通過軟件編程來完成線性碼轉換成A律。在主程序中通過A/D抽樣量化得到線性編碼,再由編碼表通過軟件計算得到8 bit A律編碼,其中最高位為符號位,第6 bit到第4 bit為段落碼,低4 bit為段內碼。將8 bit的壓縮結果存儲到系統RAM中進行緩存,根據抽樣率、語音存儲時間以及系統RAM的容量設置語音存儲緩沖區的大小,待緩沖區存滿后,將緩沖區內的數據進行解壓縮,然后輸出到SPEAKER接口輸出。

4 系統實驗結果

硬件調試成功后,使錄音時間達到5 s左右。通過CCS觀察數據圖形,圖6為壓縮前的語音信號波形,圖7為壓縮后的語音信號波形;通過回放,試聽解壓后語音信號無明顯失真。實驗結果說明系統成功實現了語音信號的壓縮存儲。

本文所介紹的MS320C5402與TLC320AD50C的組成語音壓縮存儲系統,接口電路簡單,編程方便,且程序代碼已在CCS3.1開發環境上得到驗證。

參考文獻

[1] 宋依青,何松.一種基于DSP語音信號線性與非線性量化相互轉換的新方法[J].微電子學與計算機,2008(11):36-39.

[2] 徐速.基于DSP的實時語音壓縮[J].微計算機信息,2007(2):61-64.

[3] 李利.DSP原理及應用實用技[M].北京:中國水利水電出版社,2004:200-210.

[4] TLC320ADC/TLC320AD52C Data Manual. Texas Instruments,2002.

評論