嵌入式系統中DRAM控制器的CPLD解決方案

存儲器是嵌入式計算機系統的重要組成部分之一。通常采用靜態存儲器,但是在系統需要大容量存儲器的情況下,這種方式將使成本猛增。如果采用DRAM存儲器,則可以大幅度降低系統設計成本;但DRAM有復雜的時序要求,給系統設計帶來了很大的困難。

本文引用地址:http://www.j9360.com/article/152121.htm為了方便地使用DRAM,降低系統成本,本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術,并使用VHDL語言設計實現DRAM控制器。

一、80C186XL RCU單元的資源

80C186XL的BIU單元提供20位地址總線,RCU單元也為刷新周期提供20位地址總線。80C186XL能夠產生刷新功能,并將刷新狀態編碼到控制信號中。

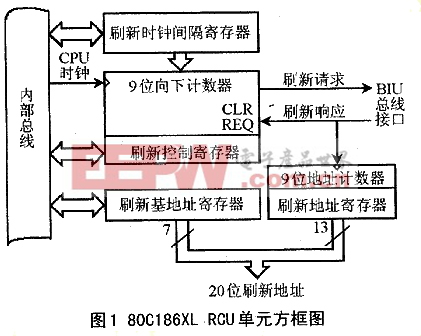

圖1是RCU單元的方框圖。它由1個9位遞減定時計數器、1個9位地址計數器、3個控制寄存器和接口邏輯組成。當RCU使能時,遞減定時計數器每一個CLKOUT周期減少1次,定時計數器的值減為1時,則產生刷新總線請求,遞減定時計數器重載,操作繼續。刷新總線周期具有高優先級,旦80C186XL總線有空,就執行刷新操作。

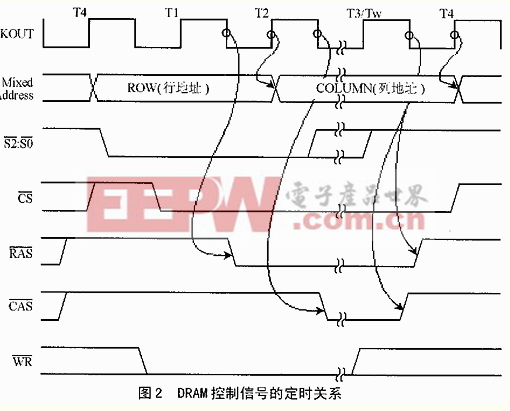

設計者可將刷新總線周期看成是“偽讀”周期。刷新周期像普通讀周期一樣出現在80C186XL總線上,只是沒有數據傳輸。從引腳BHE/RFSH和A0的狀態可以判別刷新周期,如表1所列。刷新總線周期的時序要求如圖2所示。

表1 刷新周期的引腳狀態

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論