DSP處理器與FLASH存儲器的接口技術

DSP是針對實時數字信號處理而設計的數字信號處理器,由于它具有計算速度快、體積小、功耗低的突出優點,非常適合應用于嵌入式實時系統。

本文引用地址:http://www.j9360.com/article/148308.htmFLASH存儲器是新型的可電擦除的非易失性只讀存儲器,屬于EEPROM器件,與其它的ROM器件相比,其存儲容量大、體積小、功耗低,特別是其具有在系統可編程擦寫而不需要編程器擦寫的特點,使它迅速成為存儲程序代碼和重要數據的非易失性存儲器,成為嵌入式系統必不可少的重要器件。DSP與FLASH存儲器的接口設計是嵌入式系統設計的一項重要技術,本文以基于三個C6201/C6701 DSP芯片開發成功的嵌入式并行圖像處理實時系統為例,介紹這一設計技術。

1 C6201/C6701新一代DSP處理器

1.1 C6201/C6701的特點及外部存儲器接口EMIF

C6201為通用32位定點DSP處理器,C6701為通用32位浮點DSP處理器,它們采用并行度很高的處理器結溝,從而具有許多突出的特點:

DSP核采用改進的超長指令字(VLIW)體系結構和多流水線技術,具有8個可并行執行的功能單元,其中6個為ALU,兩個為乘法器,并分成相同功能的兩組,在沒有指令相關情況下,最高可同時執行8條并行指令; ·具有32個32位通用寄存器,并分成兩組,每組16個,大大加快了計算速度;

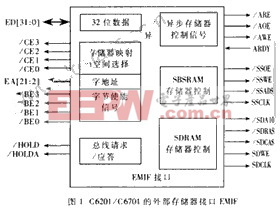

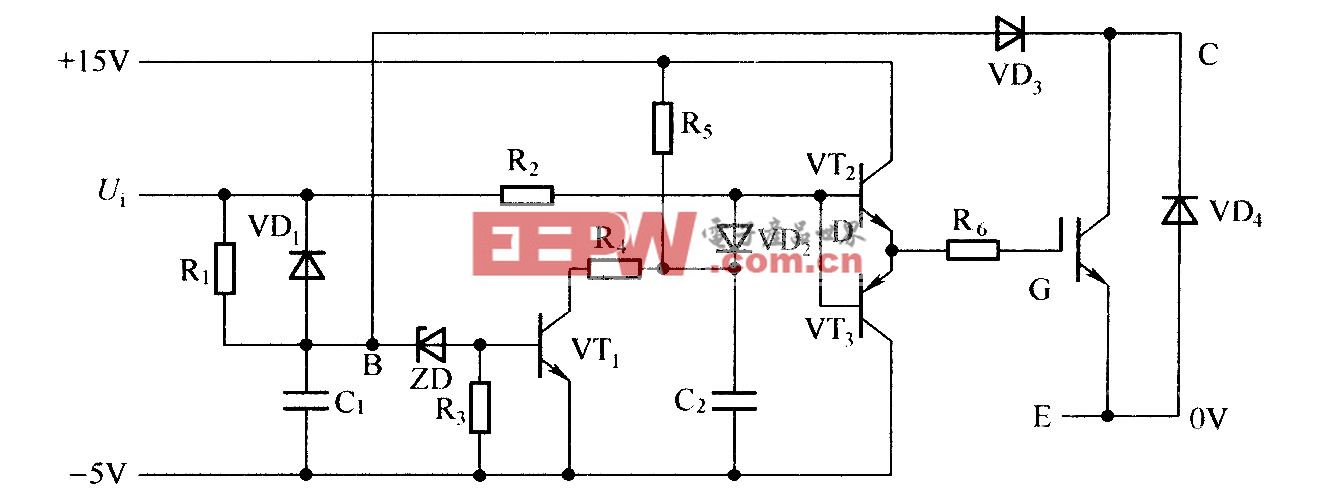

片上集成了大容量的高速程序存儲器和數據存儲措,最高可以200Mbit/s的速度訪問,并采用改進的多總線多存儲體的哈佛結構。程序存儲器為64K字節、256位寬.每個指令周期可讀取8個指令字,還可靈活設置為高速CACHE使用;數據存儲器采用雙存儲塊,每個存儲塊又采用多個存儲體,可靈活支持8/16/32位數據讀寫。C6701還可支持64位訪問,每個時鐘可訪問雙32位故據.C6701還可訪問雙64位IEEE雙精度浮點數據; 片上集成了32位外部存儲器接口EMIF,并且分成4個時序可編程的空間(CE0、CEl、CE2、CE3),可直接支持各種規格SDRAM(除CEl空間外)、SBSRAM、SRAM、ROM、FLASH、FIFO存儲器。同時,CEl空間還可直接支持8/16位寬的異步存儲器讀訪問,EMIF接口信號如圖1所示;

片上集成了4個主DMA控制器和一個輔助DMA控制器:

片上集成了兩個32位多功能定時器;

片上集成了兩個多通道通用串行通訊口;

片上集成了16位宿主機HPI端口,與EMIF端口一起。可支持構成并行多處理器系統;

片上集成的鎖相循環PLL電路,具有4倍頻外部時鐘的功能,從而在外部可采用較低的時鐘電路,而在片內可高頻(120MHz、150MHz、167MHz、200MHz)地進行計算;

片上集成了符合IEEE標準的JTAG在系統仿真接口,大大方便了硬件調試;

具有一個復位中斷,一個非屏蔽中斷,4個邊沿觸發的可編程的可屏蔽中斷;

雙電源供電,內核電源為1.8V,外圍設備電源為3.3V,功耗低于1.5W;

采用352BGA小型球柵陣列封裝,體積很小;

具有豐富的適合數字運算處理的指令集,并且所有的指令為條件轉移指令。

C6201/C6701高度的并行結構特點、高速的時鐘頻率使其具有高達1600MIPS和400MMAC的運算能力,比通常使用的DSP計算速度快十幾倍,甚至幾十倍,再加上其具有并行執行、多功能、多任務的能力和豐富的指令集以及體積小、功耗低、易于使用的特點,使它非常適合在嵌入式實時系統中應用;同時TI公司開發了高效的C編譯器和多功能的集成開發系統CODE COMPOSER STUDIO(簡稱CCS)以及高性能的仿真器,大大簡化程序代碼的編寫與調試。

1.2 C620I/06701的引導工作方式

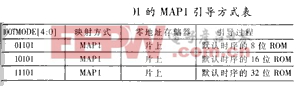

在加電后,C6201/C6701可采用直接從零地址(只能為外部存儲器)開始執行程序的不引導方式工作;也可采用輔助DMA先自動從宿主機HPI端口或外部CEl空間(8/16/32位ROM)加載64K字節程序至零地址(片上存站器或外部存儲器),然后再從零地址開始執行程序的引導方式工作。C6201/C6701的這些工作方式由上電復位時5個引導方式管腳BOOTMODE[4:0]的信號電平決定,這些電平信號還決定地址映射方式是采用某種類型、速度的外部存儲器為零地址的MAPO方式,還是采用片上程序存儲器為零地址D6 MAPl方式。這種結構特點大大增加了系統設計的靈活性。在引導工作方式中,當零地址為片上程序存儲器時,程序直接從高速256位寬的片上程宇存儲器并行執行,能充分發揮DSP的高速性能;而其它工作方式中,程序是從外部慢速32位寬的存儲器開始出行執行。因此,基于C6000的嵌入式系統一般采用引導三片上程序存儲器執行的工作方式,如表1所示。

2 FLASH存儲器MBM29LV800BA

2.1 MBM29LV800BA介紹

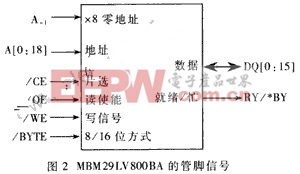

MBM29LV800BA是FUJITSU公司生產的1M×8/512K×l6位的FLASH存儲器,其管腳信號如圖2所示。/BYTE為×8或×16工作方式配置管腳(/BYTE接低時為×8方式,地址線為[A-1,A0,…A18]共20根,數據線為DQ[0:7],數據線高8位不用;/BYTE接高時為×16方式,地址線為A[0:18]共19根,A-1,不用,數據線為DQ[0:15]);RY/*BY為表示FLASH就緒或忙的管腳(它是集電極開路引腳,多個RY/*BY管腳可通過上拉電阻直接線與連接)。

MBM29LV800BA具有許多特點,主要如下

單電源3.0V讀、編程寫入、擦除;

與JEDEC標準的命令集和引腳分布兼容;

增加了快速編程寫人命令,寫入僅需兩個總線周期;

具有至少100 000次的編程寫入/擦寫壽命;

靈活的扇區結構支持整片內容擦除、任一扇區內容擦除、相連續的多扇區內容并行擦除;

具有嵌入式編程寫入算法,可自動寫入和驗證寫入地址的數據;

具有嵌入式擦除算法,可自動預編程和擦除整個芯片或任一扇區的內容;

具有數據查尋位和切換位,可以通過軟件查尋方法檢測編程寫入/擦除操作的狀態;

具有RY/*BY管腳,可以通過硬件方法檢測編程寫入/擦除操作的狀態;

自動休眠功能,當地址保持穩定時,自動轉入低功耗模式;

具有低電壓禁止寫入功能;

具有擦除暫停/擦除恢復功能,

2.2 MBM29LV800BA的主要命令及嵌入式算法

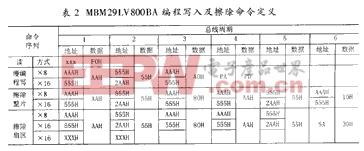

MBM29LV800BA的編程寫入及擦除命令如表2所示。其中,X為十六進制數字的任意值,RA為被讀數據的FLASH地址,RD為從FLASH地址RA讀出的數據,PA為寫編程命令字的FLASH地址,PD為編程命令宇,SA為被擦除內容的扇區地址。 MBM29LV800BA具有嵌入式編程寫入和擦除算法機構,當向FLASH寫入數據內容或擦除其扇區內容時,需要根據相應的算法編程才能完成。其編程擦除算法流程為:首先寫編程擦除命令序列;然后運行數據測試算法以確定擦除操作完成;其編程寫入算法流程為:程序開始,首先驗證寫入扇區是否為空,不空則運行擦除算法;然后運行編程寫入算法,寫編程寫入命令序列,再運行數據測試算法或查詢RY/*BY管腳信號以確定該次操作完成。地址增1繼續上述過程,否則結束操作;數據測試算法主要是測試DQ7和DQ5位的數據變化,以確定泫次操作是進行中、完成、還是失敗。

評論