基于Xilinx ISE的DDR SDRAM控制器的設計與實現

在高速信號處理系統中,需要緩存高速、大量的數據,存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器,它采用雙倍數據速率結構來完成高速操作。DDR SDRAM一個時鐘周期只能傳輸一個數據位寬的數據,因此在相同的數據總線寬度和工作頻率下,DDR SDRAM的總線帶寬比DDR SDRAM的總線帶寬提高了一倍。

本文引用地址:http://www.j9360.com/article/128748.htmDDR SDRAM控制器工作原理

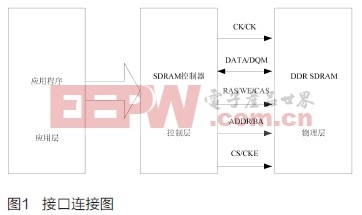

DDR SDRAM也是利用內部電容的電荷來記憶數據信息的,但電容的電荷會隨著時間而泄露,所以要在數據信息變得難以辨認之前完成數據刷新(更新),也即將數據讀出(但并不送到芯片管腳上)再寫入,其一般是周期性的,整個存儲器進行一次刷新的時間間隔為刷新周期。在刷新期間,不允許進行數據的讀寫操作。SDRAM的存儲體是按照行列組織的二維矩陣,而刷新操作按行進行,每次對一行的數據同時讀出、放大、整形和再寫入。根據標準規定,DDR SDRAM的每一行都必須在64ms以內刷新一次。DDR SDRAM有自動刷新和自刷新兩種刷新模式,且在每次突發讀取時,都會自動預充電。DDR SDRAM芯片在上電后必須由一個初始化操作來配置DDR SDRAM的模式寄存器,模式寄存器的設置決定了DDR SDRAM的刷新模式。系統上電復位,SDRAM進入持續約200ms的初始化階段之后,首先利用PCH指令對1個或4個BANK進行預充電,然后利用REF指令進行8次自動刷新,最后利用MRS指令配置DDR SDRAM進入所需工作模式,至此初始化階段完成。其后進行數據存取操作,首先利用ACT命令打開一行(也稱行有效),然后利用RD或WR命令進行單個讀寫或突發讀寫,一行完成要用PCH指令關閉該行,開始下一行數據存取操作依次循環,直至完成所有工工作。BANK激活命令后必須等待大于tCRD(SDRAM的RAS到CAS的延遲指標)時間后,發出寫命令。CL(CAS潛伏期)個工作時鐘,要向SDRAM發出預充值命令(PRECHARGE)命令,關閉已激活頁。等待tRP時間關閉已激活頁。SDRAM的基本寫操作也需要控制線和地址線相配合發出一系列命令完成。先發出激活命令(ACTIVE),并鎖存相應BANK地址(BA0,BA1)和行地址(A0~A12給出)BANK激活命令必須大于tRCD的時間后,發出寫命令字寫命令可以立即寫入,需寫入數據據依次送到DQ(數據線)上。在最后一個數據寫入后延遲tWR時間。發出預充值命令,關閉已激活頁。等待tRP時間后,可以展開下一次操作。寫操作分為突發寫和非突發寫兩種。突發長度同讀操作。寫操作控制時序如圖1所示,讀操作所等待的時鐘個數由tRCD、tRP、tWR的最小值和工作周期決定。

存儲器相關文章:存儲器原理

電荷放大器相關文章:電荷放大器原理

評論