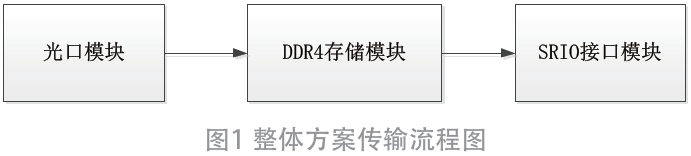

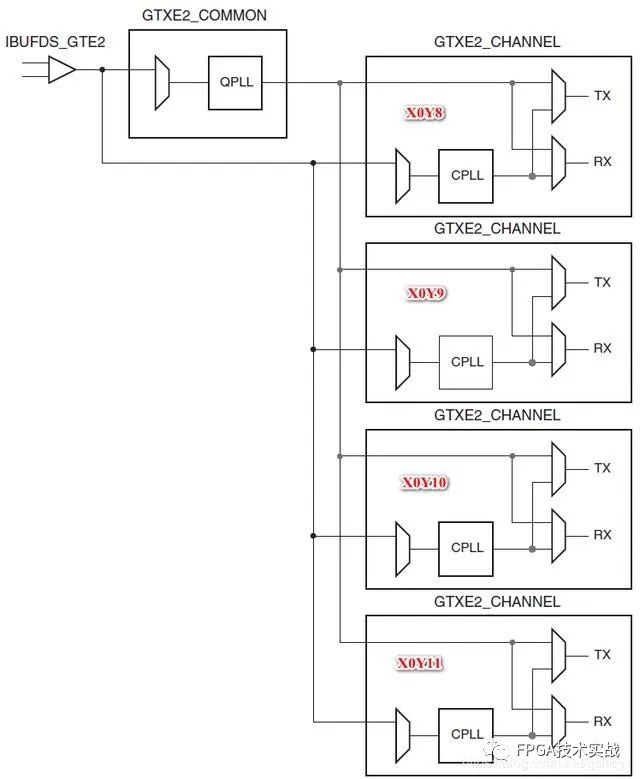

- 5G通信的主要特征包括“高速率、大帶寬”,為了滿足高速率、大帶寬數據的傳輸要求,需要一種存儲技術對數據進行存儲。本文就存儲技術結合DDR4協議,設計了一種DDR4傳輸機制,本研究采用高性能的XCVU9P系列的FPGA芯片作為控制芯片,使用其內部自帶的DDR4 SDRAM(MIG)IP核進行例化核設計。經過驗證,實現在250 MHz時鐘下對DDR4 SDRAM的讀/寫操作,數據無丟失,能夠保證高速率、大帶寬數據正常傳輸,該傳輸機制具有良好的可靠性、適用性及有效性。

- 關鍵字:

DDR4 高速率 大帶寬 FPGA 202108

- 針對5G毫米波通信宏基站、微基站等設備的研發、生產、預認證、維修保障等測試需求,設計一款可應用于“5G新基建”通信設備產業鏈多環節所需儀表的高效多速率信號接收機處理模塊。采用先進的并行多相濾波技術和任意速率比FFT處理技術,基于FPGA算法平臺實現毫米波5G接收機多路信號接收時域/頻域并行變速率處理邏輯電路,提高5G復雜波形接收機信號解析的實時性。實驗結果表明,該電路能高效完成5G復雜波形接收機信號的時域/頻域解析,適合作為毫米波5G接收機多速率數據處理實施方案,滿足毫米波5G接收機的功能設計要求。

- 關鍵字:

FPGA 5G 毫米波 接收機 202105

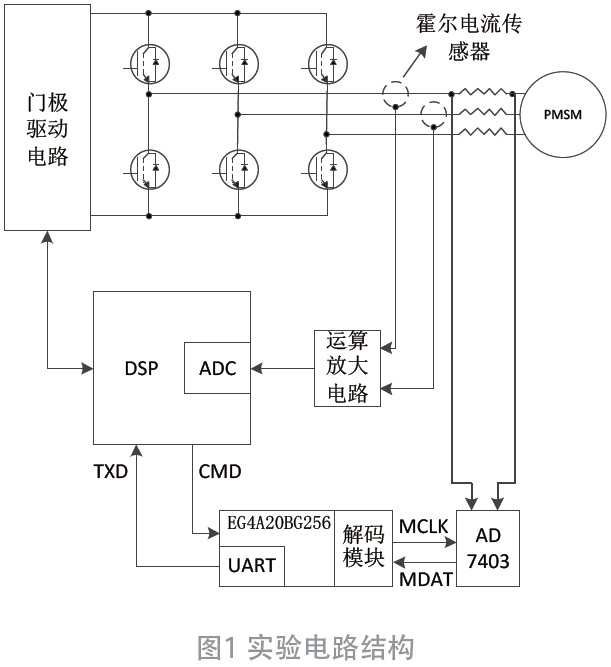

- AD7403是一種Σ-Δ型模數轉換器,廣泛應用于需要電氣隔離的伺服控制電機相電流采集場合。EG4A20BG256是一種國產FPGA,適用于伺服控制系統信號采集﹑接口擴展等應用場景。本文基于EG4A20BG256 FPGA設計了AD7403模數轉換器接口電路,采集永磁同步電機相電流,并與伺服控制電路內霍爾電流傳感器和DSP采樣結果進行了對比。結果表明,EG4A20BG256 FPGA可以通過AD7403模數轉換器實現對永磁同步電機相電流的準確采集。

- 關鍵字:

AD7403 EG4A20BG256 FPGA DSP 永磁同步電機 202105

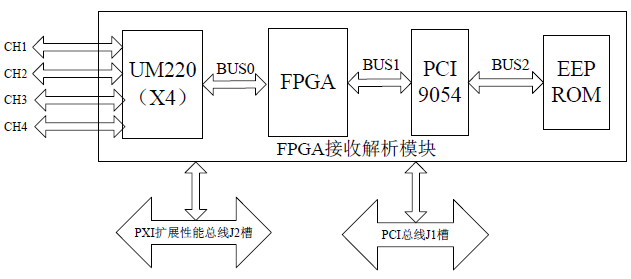

- 設計并實現了一種BD/GPS衛星導航信號多通道隔離轉換測量顯示系統。該系統將一路輸入的BD/GPS信號通過功分器轉換為等量的四路隔離輸出信號,經FPGA解析后實時顯示在電腦屏幕上,為BD/GPS信號的使用提供直觀的數據基礎。

- 關鍵字:

BD/GPS FPGA 功分器 隔離 202107

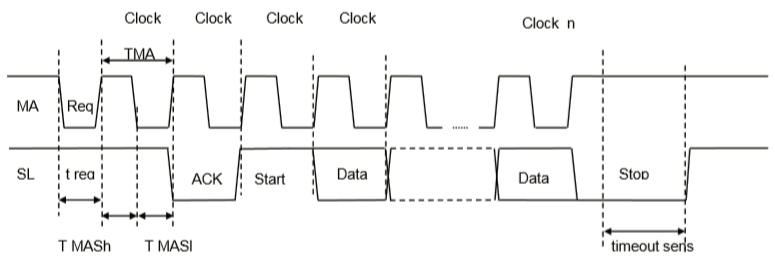

- 摘要:針對目前BiSS協議編碼器數據讀取多采用FPGA實現的實際情況,文中介紹一種基于XMC4500微控制器的BiSS協議編碼器數據讀取實現方案。采用該方案,可將使用BiSS協議編碼器的伺服系統控制電路常用的DSP+FPGA雙控制器架構方式簡化為XMC4500單控制器方式,在一定程度上降低了硬件成本和開發難度。用該方案采集BiSS協議編碼器數據的實物平臺,使用LabVIEW顯示對讀取的數據,并與電機自帶增量編碼器值進行對比,同時記錄BiSS協議編碼器實際數據波形圖,結果表明,該方案具有較高的采樣速率和較好

- 關鍵字:

202106 BiSS XMC4500 DSP FPGA LabVIEW

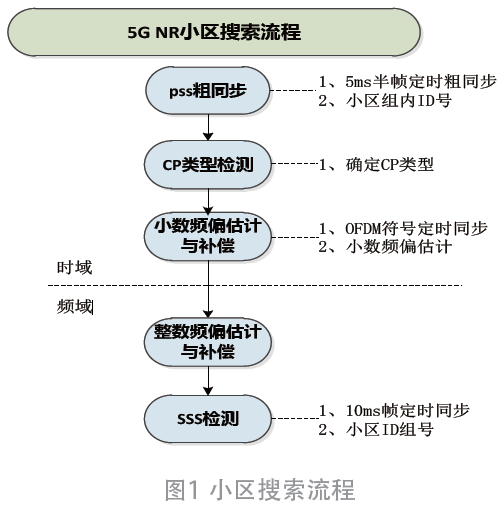

- 隨著移動通信的高速發展,5G NR通信已經進入我們的日常生活,5G系統對信息傳輸制訂了全新標準,基于5G NR的小區搜索相對于長期演進(LTE)而言,對同步信號進行了重新定義。文章詳細分析了5G NR系統的主輔同步信號(PSS&SSS),對其新增內容進行了研究,提出了適用于5G NR系統的小區搜索算法,使用MATLAB軟件對該算法的性能進行了仿真分析,最后在FPGA上實現開發應用。

- 關鍵字:

5G NR FPGA 小區搜索 PSS SSS 202105

- 邊緣運算主要包含以下四個部分,低時延、AI算力、低功耗以及安全和保密,這四者是邊緣自主非常重要的組成部分,也是邊緣區別于工業和IoT的一個主要特點,也就是用運算資源來支持邊緣的自主,使它能夠獨立于云端。 賽靈思Versal AI Edge系列資深產品線經理 Rehan Tahir賽靈思Versal AI Edge系列高級產品線經理Rehan Tahir指出,當賽靈思在2018年引入Versal ACAP的時候,首先推出的是Versal Core和Prime系列,用于云端和網絡,然后推出了Vers

- 關鍵字:

賽靈思 FPGA ADAS

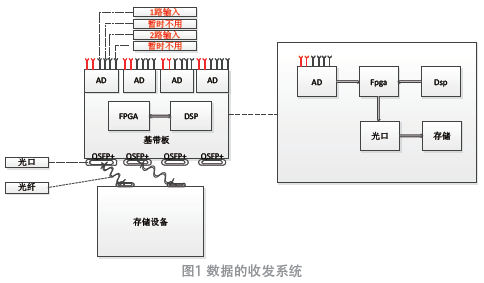

- 隨著通信技術的快速發展,5G已經正式商用,5G的6G以下波段對傳輸有很高的要求,在6G以上的毫米波段要求的信號帶寬更大,數據傳輸速率更高,高速大帶寬信號要求基帶信號處理的速度將大大增加,對極高速數據流的實時處理和解析使測試變得更加困難,本文主要是研究與設計毫米波基帶數據的傳輸與實現:前端DA的研究與設計、傳輸鏈路的FPGA實現以及毫米波數據的DSP接收處理過程,最后把實現流程成功應用到5G測試儀表之中,驗證了設計的正確性。

- 關鍵字:

202104 毫米波 FPGA 基帶數據 DSP

- 作為第四任賽靈思的CEO,上任三年多的Victor Peng在交易后首次面對中國的媒體時,除了總結自己上任三年來的成績之外,更是重點的回應了對合并后企業的愿景

- 關鍵字:

賽靈思 FPGA AMD

- 引言:本文我們簡單介紹下Xilinx?FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。管腳位置約束: set_property PAKAGE_PIN “管腳編號” [get_ports “端口名稱”]管腳電平約束: set_property?IOSTANDARD “電壓” [get_ports “端口名稱”]舉例:set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]set_property IOSTANDARD LVCMOS33

- 關鍵字:

xilinx fpga

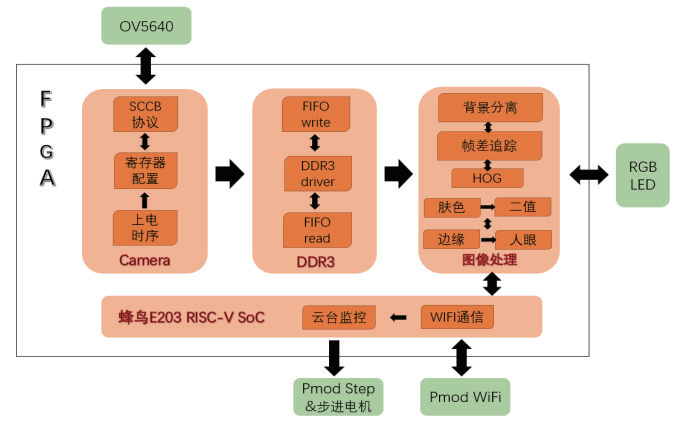

- 本設計基于FPGA硬件平臺實現了對一個區域場景的入侵檢測與追蹤識別,對檢測到的運動物體作出人與動物的區分,能夠通過無線方式發送警報,且系統檢測具有較高的魯棒性。本系統以FPGA為核心單元,主要由五個模塊構成:OV5640攝像頭模塊,DDR3數據儲存模塊、圖像數據處理模塊、蜂鳥E203 RISC-V SoC片上系統。系統整合與調試結果顯示,本設計在FPGA上采用了合適的算法搭建系統,能對視頻圖像中的運動目標進行實時、準確的識別與追蹤。

- 關鍵字:

Robei FPGA 動態目標追蹤 實時圖像處理 背景差分法 202103

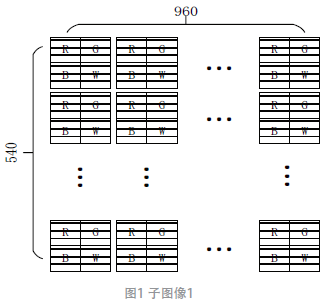

- 尺寸與性能是微顯示系統的重要衡量指標,為了實現微顯示系統的小尺寸與高性能,通過對視頻圖像數據的實時處理計算,實現圖像的動態子像素融合,在FPGA上實現了電路,配合顯示芯片完成視頻圖像顯示。點屏的對比效果顯示,在節省了FPGA中74%存儲資源的同時提高了顯示芯片接近四倍的顯示分辨率,等效到顯示系統中能減少80%的芯片面積。這種微顯示系統同時解決了微型化與高分辨率的技術難關,非常適合應用于微顯示相關領域。

- 關鍵字:

微顯示系統 微顯示芯片 分辨率 子像素融合 FPGA 202103

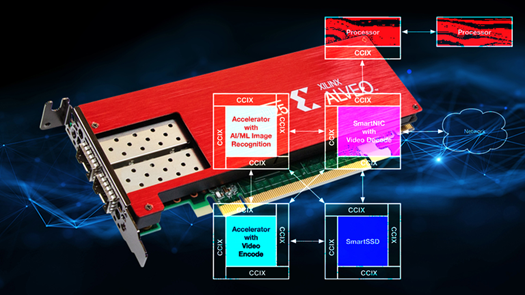

- 與普通的 NIC 不同,SmartNIC 將會對 PCIe 總線提出更高的要求。CXL 和 CCIX 等第五代 PCIe 和協議在此背景下應運而生。不久之后,我們將能共享一致性存儲器、高速緩存,并建立多主機點對點連接。 正文:過去三十年間,基于服務器的計算歷經多次飛躍式發展。上世紀 90 年代,業界從單插槽獨立服務器發展到服務器集群。緊接著在千禧年,產業首次看到雙插槽服務器,再后來,多核處理器也問世了。進入下一個十年,GPU 的用途遠遠超出了處理圖形的范疇,我們見證了基于FPGA的加速器卡的興起

- 關鍵字:

PCIe 5 FPGA 賽靈思

- 2020年11月18日,在英特爾FPGA技術大會上,英特爾發布了全新可定制解決方案英特爾? eASIC N5X,幫助加速5G、人工智能、云端與邊緣工作負載的應用性能。該可定制解決方案搭載了英特爾? FPGA兼容的硬件處理器系統,是首個結構化eASIC產品系列。英特爾? eASIC N5X通過FPGA中的嵌入式硬件處理器幫助客戶將定制邏輯與設計遷移到結構化ASIC中,帶來了更低的單位成本,更快的性能和更低的功耗等好處。英特爾? eASIC N5X器件作為具有創新性的新產品,與FPGA相比最高可降低50%的核

- 關鍵字:

eASIC 英特爾 FPGA

fpga:quartusⅡ介紹

您好,目前還沒有人創建詞條fpga:quartusⅡ!

歡迎您創建該詞條,闡述對fpga:quartusⅡ的理解,并與今后在此搜索fpga:quartusⅡ的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473