5G毫米波基帶數據傳輸的研究與實現

0 引言

隨著全球移動通信技術向著網絡化和寬帶化趨勢發展,5G 商用的步伐已經到來。5G 商用的基站和手機也已經開始部署與批量生產。現在,儀表除了能夠分析6 GHz 以下頻率的信號以外,還需要分析微波、毫米波等波形。毫米波傳輸的技術難點主要在于5G 極高速的傳輸速率導致信號帶寬和基帶信號處理速度都將大大增加,對極高速數據流的實時處理和解析使得測試變得更加困難,作為測試技術的先行者,測試儀表5G 功能毫米波測試技術開發也已提上日程[1]。

毫米波現在的信號帶寬已經達到400 MHz,如此寬的信號帶寬需求對信號的采樣率提出了很高的要求,前端的AD 處理是信號成功采集的第一步。隨著技術的快速發展,AD 處理能力也得到了較高提升,具有大于5 Gsps 采樣處理能力的采集單元也已經問世,為毫米波的成功實現奠定了基礎。實現過程中選定的AD 芯片一般具有較高采樣率,簡化了RF 信號到數字信號的接口要求。內部集成數字下變頻器(DDC),以及數控振蕩器(NCO)和輸出數據提供了串行連接可配置的JESD204B 的接口。

基帶接收處理模塊是滿足多通道接收、不同系統帶寬、不同子載波間隔、多用戶基帶接收的指標要求,完成參數靈活可配單用戶、多用戶基帶信號接收功能,滿足5G 終端的低延時、高效率、高質量的處理能力。FPGA 是現階段實現采用的主流方式,具有處理較強的數字能力,設計采用了Xilinx 公司的FPGA 芯片作為主要的實現平臺。

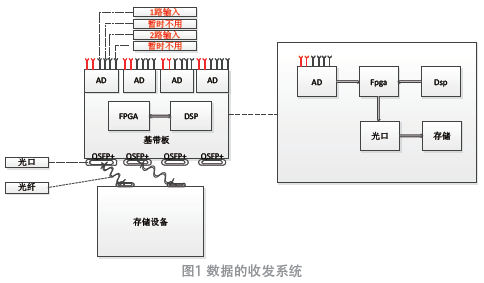

為了實現基帶數據成功采集后的離線分析,采用FPGA 與DSP 互聯功能把采集的數據經乒乓模式寫入DSP,由DSP 隨機取數進行離線分析,突破了高速信號不易實時分析的難題。毫米波的接收系統如圖1 所示。

作者簡介:袁行猛(1988—),男,工程師,研究方向:信號與信息處理。

1 系統架構

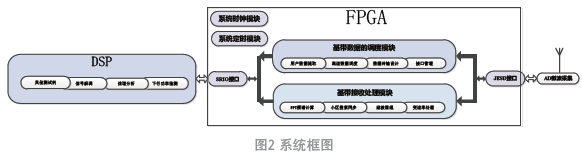

基于乒乓切換的5G 毫米波基帶數據傳輸系統如圖2 所示,該系統實現了射頻單元采集的毫米波數據到FPGA 的傳輸,高速數據經過處理緩存到DSP 中作為數據解析使用的數據通路。其中,數據采集部分使用高精度、高采樣率AD 芯片,通過高速JESD 接口傳輸到FPGA 中,為了方便數據的處理與存取,要設計傳輸機制能正確存儲數據的DSP。5G 毫米波的存儲主要有兩個難點;①高速數據接口設計:在收端,數據轉換模塊將高速采樣的數據處理成指定速率的IQ 數據;②獲取高速的IQ 數據后通過調度保證數據不丟失連續寫入DSP 中。本次研究成功設計出高速接口交互與數據調度算法成功解決了這兩個難題,并應用到測試儀表中。

2 5G物理層概述

物理層資源的靈活配置是5G 系統物理層資源的重要特征[2]。靈活的幀結構、時頻資源的靈活配置以及靈活的時隙配置確保了5G 能滿足不同業務需求,適應不同應用場景。

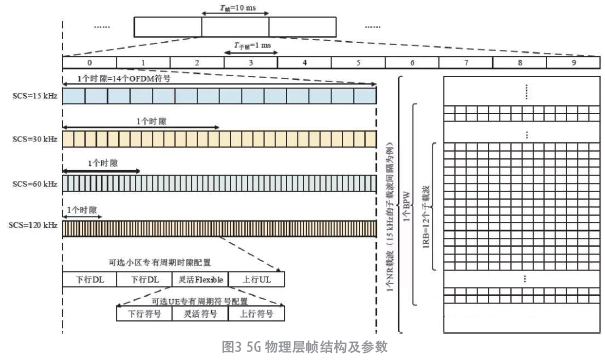

圖3 為5G NR 的幀結構及相關參數。

在時域上,常規CP 下,每個時隙包含了14 個OFDM符號;在頻域上,12 個子載波構成一個資源塊(Resource Block,RB), 多個連續的RB 構成一個帶寬部分(Bandwidth Part,BWP), 多個BWP 構成一個NR 載波。

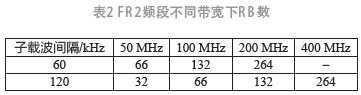

NR 支持從1 GHz到毫米波段范圍的頻譜,R15 中定義了兩個頻率范圍(FR):FR1:450 MHz-6 GHz,通常指Sub-6 GHz,最大帶寬為100 MHz;FR2:24.25 GHz-52.6 GHz,通常指毫米波,最大帶寬為400 MHz。

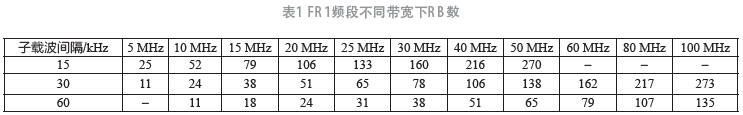

基于終端的能力,3GPP 限制單個小區有效子載波數不超過3 300(FFT 點數不超過4 096),因此不同子載波間隔情況下支持的小區最大帶寬不一樣,每種帶寬配置下的最大RB 數如表1。

3 數據傳輸設計

由上節介紹可知,5G 毫米波的信號帶寬已達400 MHz,對于接收來說,這需要前端射頻具有較高采樣率。本次設計采用491.52 MHz 采樣率進行數據的采集[3]。根據5G 的參數集與幀格式可知,要想對5G信號進行分析解調需要至少10 ms 有效數據[4],因此10 ms 內的數據量已經達4 915 200 個IQ 數據,正常存取這么多數據,整個鏈路速率至少要15.7 Gb/s。設計中基帶板的DSP 接口采用SRIO 口協議,有效速率只有16 bp/s,直接傳輸已接近理論最大值,很難保存連續有效的10 ms 數據。設計中采用射頻與DSP 之間增加DDR4 作為緩存解決這一難題。

3.1 功能設計

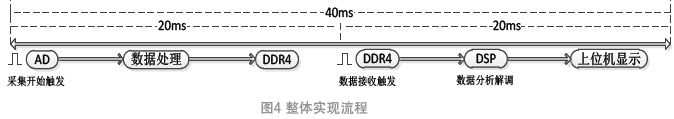

通過高采樣率AD 板卡采集5G 毫米波段信號,全部在FPGA 中處理,連續采樣的發端數據I、Q 各16 bit,組成32 bit 數據通路,對應的速率491.52 Mb/s線速率,此時的32 bit 位寬數據是一直有效數據,每10 ms 進行頻譜與時域信號處理。緊接著每20 ms 乒乓切換模式,接收采樣開始觸發信號,開始從頭采樣數據,10 ms 數據持續不斷地送入DDR4 中,DDR4 的速率最高可達1 Gb/s,速率完全可以滿足存儲需求,然后在下一個20 ms 對接收到的數據進行觸發,并把10 ms 數據持續不斷讀出到DSP,此時讀出速率可以降低,以滿足SRIO 口速率要求;把數據連續讀出到DSP,由DSP 進行部分毫米波數據分析解調,把解調結果通過網口傳給上位機顯示結果,具體實現流程如圖4 示。

3.2 算法設計

1) 乒乓緩存

把整個信號分成40 ms,其中20 ms 作為信號采集和存儲使用,另一個20 ms 作為信號的讀取、分析以及傳輸解調結果使用,由此每40 ms 一個循環,其中每20 ms 作為乒乓切換功能使用,這里主要靠FPGA 產生定時采集與接收觸發來控制整個實現流程。

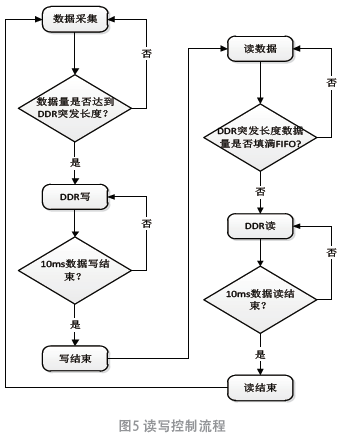

2) 數據流控制

我們考慮,由于數據采集速率很快,DDR4 的工作時鐘很高,但DDR 讀寫操作時有突發長度的要求,所以分別設計時序控制,寫操作之前放一個FIFO,要求其中數據量至少有突發長度時才往DDR 里面寫。DDR 讀操作時也同樣設計對應的時序控制,由于DDR 讀出時鐘很快,一次讀出數據量就是突發長度個數,這里同樣設計一個FIFO,當FIFO 快達到自定義滿標志時就停止從DDR 中讀出數據,具體讀寫控制流程如圖5 所示。

3) 在毫米波采集之后,需要進行數據的頻譜與時域分析,數據速率為491.52 MHz,此時需要轉化為122.88 MHz 采樣率,在rx 端的數據處理之前進行4 倍抽取處理,這里采用2 個2 級半帶抽取濾波器,處理過后的數據連續進行時頻域分析。處理過的數據進行和有效數據的組合,本設計是放到10 ms 數據頭位置,傳給DSP 之后,由DSP 識別并取出。

4 仿真驗證與實際應用

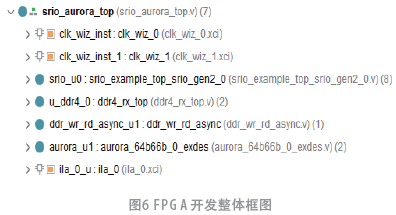

采用Vivado 2018.3 軟件進行本次開發工作,開發的FPGA 芯片型號為xcku060-ffva1156-2-i,本次設計通過上基帶板以及整個采集平臺,最終驗證本次設計的可行性。

圖6 所示是設計的整體開發框架。

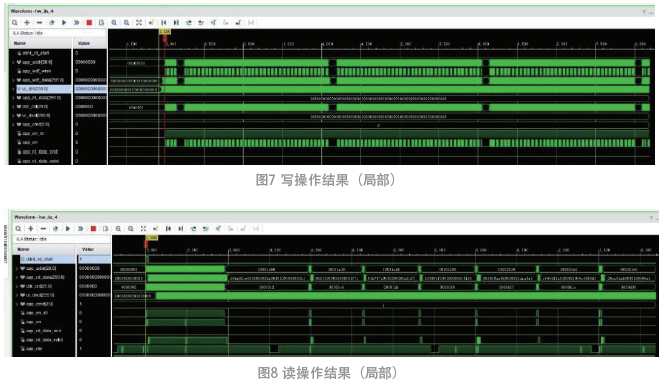

通過連接整機射頻后實際采樣,傳輸給DDR 后又讀出到DSP 的時序圖,圖7 是DDR 寫操作,圖8 是上板后DDR 的讀操作的真實結果。

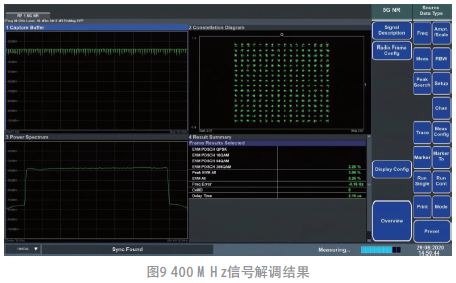

最后通過仿真傳輸給上位機顯示,如圖9 所示,5G毫米波波段,400M 帶寬信號已經正常顯示與解調,說明了設計的正確性。

通過仿真以及最終的顯示結果可以發現,通過前端AD 采樣后,經過本設計的傳輸機制,數據每40 ms 存取10 ms 有效信號,然后用20 ms 取數與分析,最終送到上位機顯示,可以發現已經正常解調,從而說明設計的功能正常,滿足5G 毫米波段400 MHz 信號的傳輸與解調。

5 結論

本研究完成了5G 毫米波基帶數據的研究與實現功能。為了構建基帶單元BBU和射頻單元RFU 之間數據通路,需將具有較高采樣率的5G 信號正常存取到DSP 用于分析解調。本設計主要研究開發了基于乒乓切換存取的機制、數據流控制機制,以及防止DDR 讀取出錯的預防機制。經過仿真和硬件驗證了傳輸的正確性,確定了本研究的可行性。

參考文獻:

[1] 何世文,黃永明,王海明,等.毫米波無線通信發展趨勢及技術挑戰[J].電信科學,2017(6):11-19.

[2] 張然.5G移動通信網絡關鍵技術研究[J].信息與電腦:網絡與通信技術,2018(3):168-169.

[3] 黃宇紅,劉盛綱,楊光,等.5G高頻系統關鍵技術及設計[M].北京:人民郵電出版社,2018.

[4] 歐洲電信標準協會IX-ETSI.5G;NR;Physical Layer;General Description(V15.0.0;3GPP TS 38.201 version 15.0.0 Release 15):ETSI TS 138 201-2018[S].2018.

[5] 同偉鋒.基于DSP+FPGA的嵌入式視頻采集系統的設計[D].西安:西安電子科技大學,2009.

(本文來源于《電子產品世界》雜志2021年4月期)

評論