5G NR小區搜索算法的研究及FPGA實現

0 引言

隨著全球移動通信技術向著網絡化和寬帶化趨勢發展,人們的社會生活方式、工作模式等方面發生了極大的改變。隨著人類對更高性能移動通信網的追求,移動通信系統也不斷更新換代。5G 通信技術應運而生,作為測試技術的先行者,測試儀表5G NR 功能的開發也提上了日程。同步技術的研究是5G 物理層中一個十分重要的課題。本文的研究工作主要集中于5G 系統下行鏈路的初始同步過程。其中,下行鏈路重點對主同步信號(primary synchronization signal,PSS)以及輔同步信號(secondary synchronization signal,SSS)的檢測方案展開研究并以FPGA 實現。本研究致力于5G NR 小區搜索算法技術研究與實現,其意義在于:在市場上,目前5G 測試儀器受到業界的關注,本課題研究的5G NR小區搜索與實現適應測試儀器市場需求,對通信測試儀器的發展提供有力支持;隨著移動產業化的不斷深入發展,測試儀器作為產業鏈的重要組成部分越來越受到業界的關注,本課題有助于促進測試儀器的發展及推廣。

作者簡介:袁行猛(1988—),男,工程師,研究方向:信號與信息處理。

1 小區搜索過程

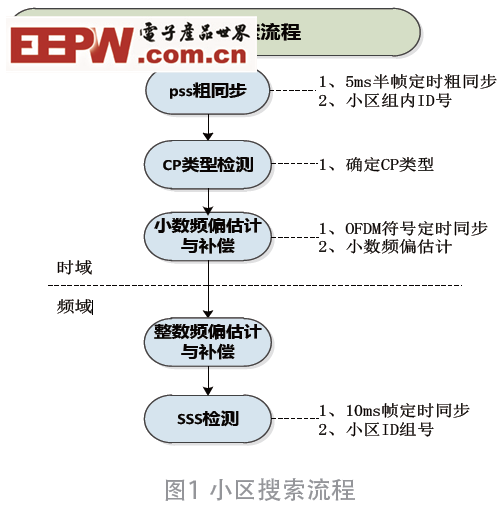

5G NR 小區搜索是指利用同步信號獲得其所在小區的ID 號以及取得與基站的時頻同步的過程。本章首先描述了5G NR 小區搜索流程,然后為使系統的整體性能達到最優,對各部分采用的不同算法進行分析和討論。小區搜索流程如圖1 所示。

如圖1 所示,接收到的射頻信號同步流程通常被分為4 個部分:粗時間同步、CP 類型檢測、頻偏估計與補償和SSS 檢測。射頻整機通過射頻端口接收到5G NR 信號,然后傳到同步模塊。粗時間同步的目的是為了找到PSS 信號的位置以此判定半幀同步,同時還能確定扇區號。CP 檢測可以確定CP 所屬類型。在頻率同步部分,先進行小數倍頻偏的估計與補償,以保證載波之間的正交性,同時取得定時精同步,經過OFDM 解調到頻域后進行整數倍頻偏估計與補償。SSS 檢測的目的是獲得10 ms 的幀定時同步,同時確定小區ID 組號。

2 5G NR小區搜索算法與仿真實現

2.1 粗同步算法

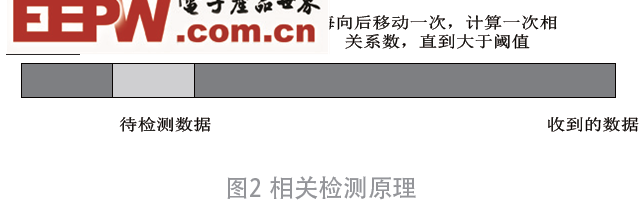

PSS 檢測算法都是基于序列相關運算的,原理如圖2 所示。滑動窗口保存了本地存儲的同步序列,在收到數據之后,從數據起始位置向后移動,每移動1 個采樣點計算1 次相關系數,當得到1 個相關峰值時,則認為這時滑動窗口和待檢測的同步序列對齊。由于PSS 有3種,所以本地需存儲3 種PSS,且在每次滑動窗口移動時計算3 組相關系數,相關峰值最大的序列則為基站發送的序列,同時確定其值。

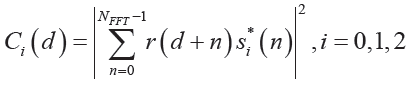

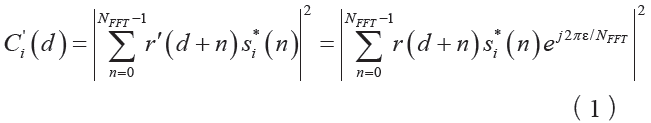

直接互相關法的本質是利用滑動搜索的方法,找到與接收信號匹配的同步序列。首先對本地的3 種PSS 序列補零后做IFFT 變換,然后分別與下采樣后的信號做滑動相關,得到3 個序列集,其中最大值所對應的序列號就是小區組內ID 號 ,最大值所在的位置就是同步序列的初始粗同步位置。由于m 序列時域互相關函數具有尖銳的峰值,所以能夠得到較為精確的同步位置。互相關函數的模值平方如下式:

,最大值所在的位置就是同步序列的初始粗同步位置。由于m 序列時域互相關函數具有尖銳的峰值,所以能夠得到較為精確的同步位置。互相關函數的模值平方如下式:

其中,“()*”表示共軛運算; NFFT 表示采樣點數;r(n)代表接收到的下采樣后的信號;s n i ( ) 是本地存儲的時域同步信號,i 取0,1,2 時分別對應 的值0,1,2;d 是起始時刻,每一時刻做1 次相關運算,得到粗同步位置d?為:d? = MAX {C d i = I ( )} , 0,1,2 。

的值0,1,2;d 是起始時刻,每一時刻做1 次相關運算,得到粗同步位置d?為:d? = MAX {C d i = I ( )} , 0,1,2 。

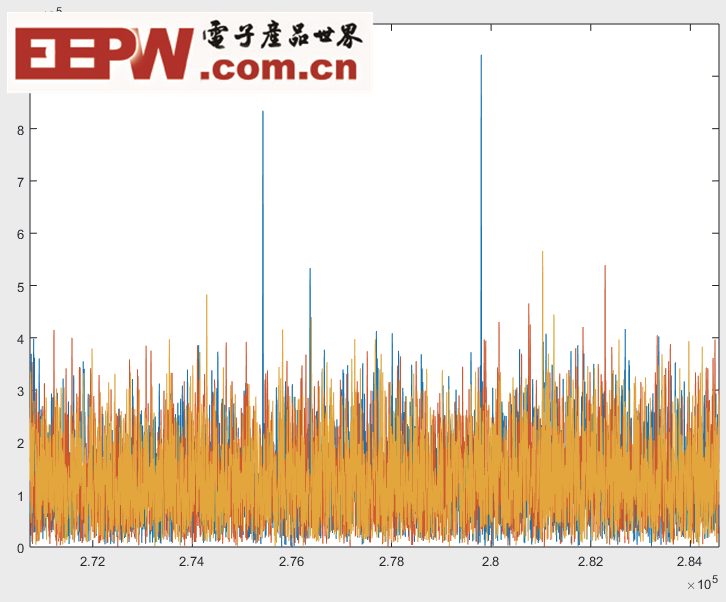

圖3 小區組內ID為0分別與1,2,3的序列時域互關性

圖3 是時域PSS 序列自相關及互相關性能仿真圖,顯而易見,PSS 序列有較好的時域相關性。通過直接互相關法可以實現對主同步信號的粗定時同步和小區組內ID 的判斷,但是該方法對頻偏的魯棒性較差。當存在頻偏ε 時,互相關函數表達式如下:

其中,r′(d + n)表示受頻偏影響的接收信號。由式(1)可以看出,由于頻偏因子e j2π ε/NFFT的存在,對不同時刻的信號都產生相位旋轉,可以使相關函數的峰值衰減,從而對定時同步正確性產生影響。

2.2 精同步算法

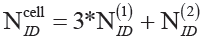

完成主同步信號檢測后,已經獲得小區組內ID 號 ,由式知

,由式知 與m0 和m1 有關,所以可通過檢測SSS序列獲得

與m0 和m1 有關,所以可通過檢測SSS序列獲得 ,進一步根據

,進一步根據 確定物理層小區ID。對于SSS 序列的檢測,既允許在時域進行,又允許在頻域進行。由于在時域做相關檢測需要對整個OFDM 符號做檢測,計算復雜度較大且易受定時估計誤差的影響,而頻域檢測只需提取127 點SSS 序列即可做相關,計算量小且定時同步誤差在頻域上對相關峰的影響不大,所以可以在頻域進行SSS 序列的檢測。

確定物理層小區ID。對于SSS 序列的檢測,既允許在時域進行,又允許在頻域進行。由于在時域做相關檢測需要對整個OFDM 符號做檢測,計算復雜度較大且易受定時估計誤差的影響,而頻域檢測只需提取127 點SSS 序列即可做相關,計算量小且定時同步誤差在頻域上對相關峰的影響不大,所以可以在頻域進行SSS 序列的檢測。

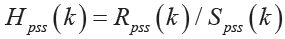

因為PSS 序列與SSS 序列在時域上只間隔1 個OFDM 符號,在頻域上處于相同的子載波位置。為了提升SSS 信號的解調性能,可以利用檢測后的PSS 信號得到信道沖擊響應,再對SSS 信號進行補償。令接收到的頻域PSS 信號為基值k ,信道估計結果可以表示為:

。

。

其中,Spss(k) 為本地頻域PSS 序列。假設接收的SSS

序列rsss(k) 經FFT 轉換到頻域為Rsss(k) ,則經過信道均衡的SSS 序列可以表示為: R'sss(k)=Rsss(k)/Hpss(k) 。

頻域SSS 序列是由2 個m 序列優選對通過異或運算組成的Gold 序列,該序列具有較好的相關性質。將R'sss(k) 與本地產生的336 條SSS 序列分別進行頻域互相關,得到:![]() ,式中i =0,1,...,335,代表此時所選擇的輔同步序列的序列號。通過相關運算的結果容易找到C(i) 中的最大值對應的序列號i,如式:

,式中i =0,1,...,335,代表此時所選擇的輔同步序列的序列號。通過相關運算的結果容易找到C(i) 中的最大值對應的序列號i,如式:![]() 。

。

根據以上分析,該序列號i 就是小區組ID 標識號 。

。

2.3 仿真結果分析

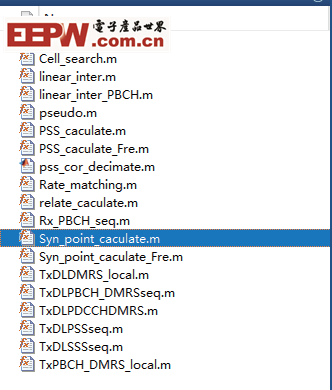

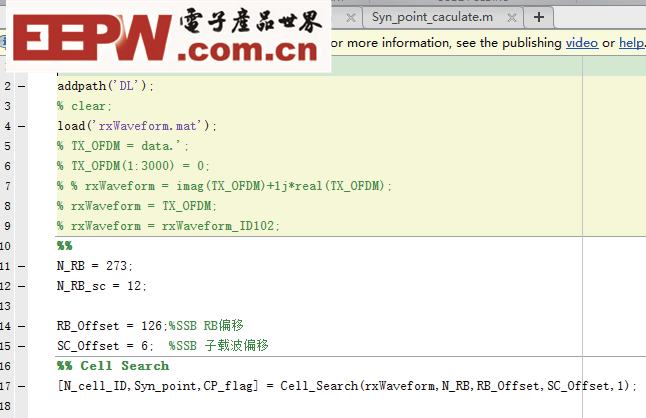

仿真軟件選用的是MATLAB R2015a,根據前章節的算法理論分析編寫仿真代碼,編寫的軟件函數架構以及主函數如圖4 所示。

圖4 軟件函數架構和主函數

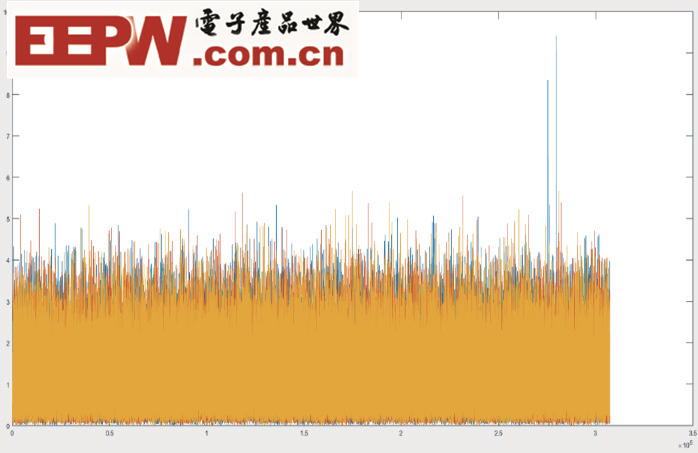

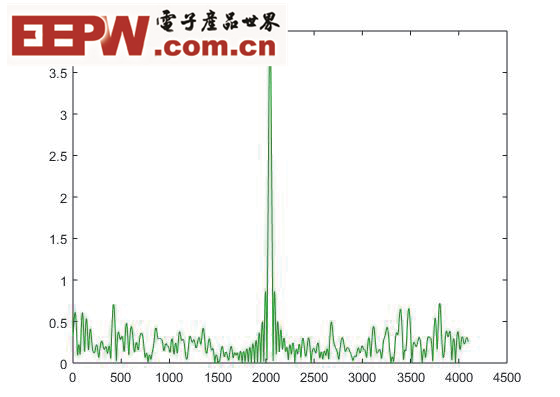

MATLAB 仿真得到的粗同步與精同步結果如圖6和圖7 所示。

圖6 粗同步結果

圖7 精同步結果

3 5G NR小區搜索算法的FPGA實現

本研究將對PSS 算法和SSS 時延優化算法進行實現,并通過硬件平臺的綜合結果對算法進行驗證。在通過FPGA 實現算法的同時,也會利用一些FPGA 技巧降低實現的復雜度,節約開發成本。本章將給出每個模塊的設計方案,整體流程和最終的硬件綜合結果。

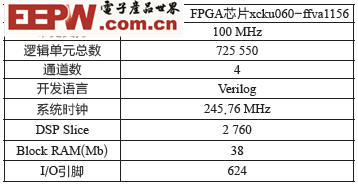

3.1 FPGA開發板的性能參數

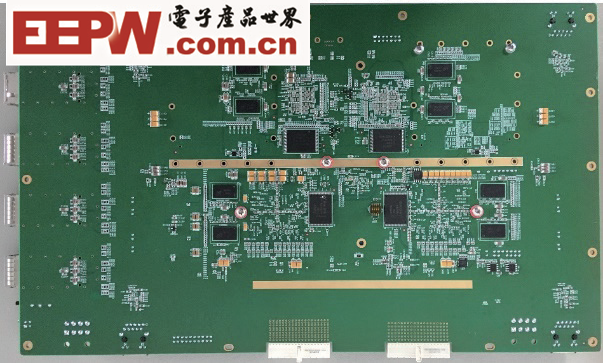

在進行FPGA 開發之前,首先要了解FPGA 開發板的性能和開發工具的使用,本節主要介紹本文采用的開發板性能參數和開發工具的能力,FPGA 開發板的參數由表1 給出,硬件設計結構如圖8 所示。

圖8 基帶板正反面

表1 開發板性能參數

開發工具采用Xilinx 的Vivado,該工具內部集成了FFT、IFFT、FIFO、RAM、乘法器等常用IP 核,可以極大降低開發難度。

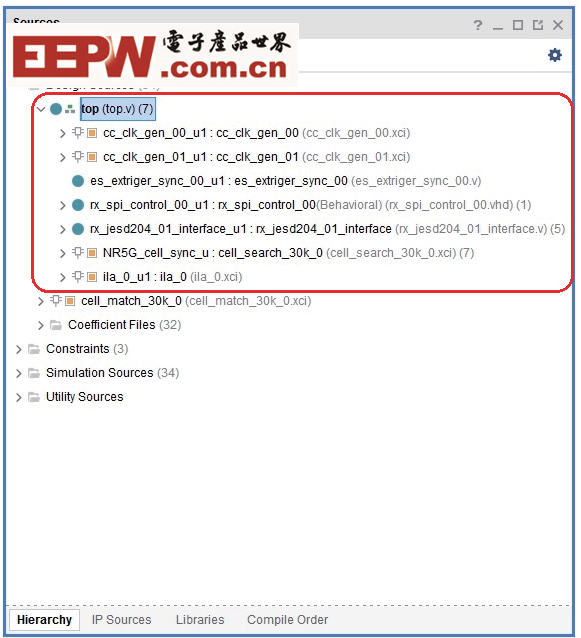

3.2 頂層模塊設計

圖9 給出了核心模塊、相關運算模塊的結構,實現中需要FPGA 進行多次遍歷與計算,模塊采用純并行設計,每個時鐘寫入1 個采樣點,每個采樣點單獨進行計算,求和處采用流水線方式進行多個復數的求和計算,整體流程時延集中在求和與計算模值,本設計中利用乘法器直接進行序列相乘得到相應結果。整體開發的程序模塊如圖9 所示。

圖9 程序整體模塊

top:設計的頂層文件;

rx_jesd204_01_interface_u1:射頻信號采集模塊,直接采集射頻信號轉換成245.76 MHz 的時鐘速率;NR5G_cell_sync_u:5G NR 小區搜索頂層模塊;小區搜索模塊是具體的實現模塊,粗同步、精同步以及各個相關運算等,如圖10 所示。

圖10 小區搜索主要模塊

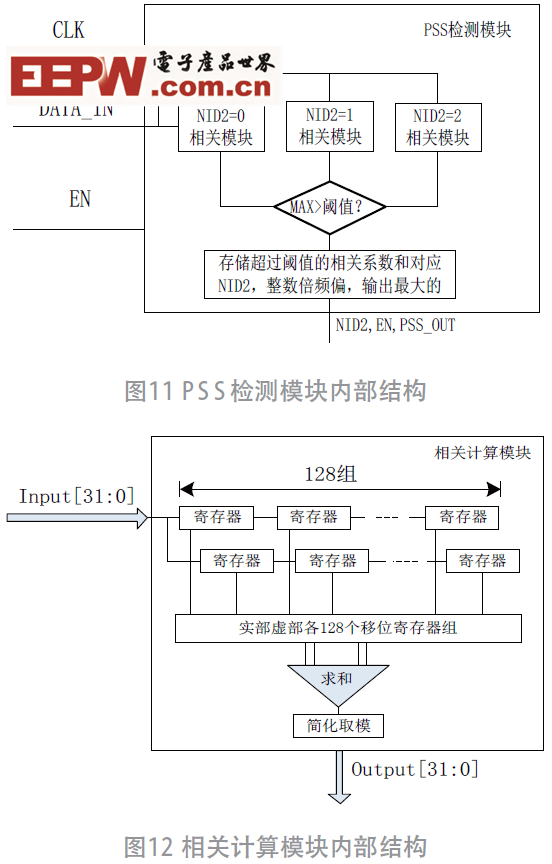

3.3 同步模塊設計

主同步信號的FPGA 開發的過程:該算法的原理在第三章已進行介紹,并且通過仿真平臺進行了性能評估,圖11 給出了PSS 檢測模塊的功能模塊結構,圖12 給出了核心模塊,該模塊存儲了量化后的本地序列。量化后的序列取值均為2 的次冪形式,在模塊的編寫過程中,需要根據每一項本地序列的量化結果進行寄存器的移位,所以實現的代碼量巨大。該模塊采用純并行設計,每個時鐘寫入1 個采樣點,每個采樣點單獨進行計算,求和處采用流水線方式進行多個復數的求和計算,整體流程時延集中在求和與計算模值。

圖12 中的輸出部分有一個簡化取模算法。取模運算涉及平方和開根號運算,在FPGA 中實現困難,需要借助cordic 算法實現,這會引入較大時延和硬件開銷。由于PSS 檢測部分只關心相關系數的大小,對相關系數較小的誤差并不敏感,因此可以利用取模的近似算法來計算。

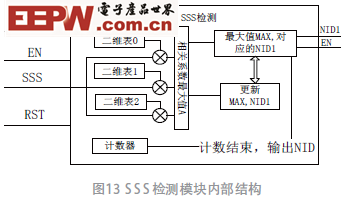

輔同步信號的FPGA 開發的過程:

SSS 檢測采用了分組并行檢測算法,該模塊的FPGA 結構如圖13 所示。將本地SSS 序列分組后進行存儲,EN 端口電平拉高后開始進行遍歷,計數器存儲當前遍歷次數,每次遍歷同時計算三組序列相關系數,得到最大值A 和對應的NID1,MAX 存儲了相關系數最大時對應的NID1,遍歷過程中不斷更新。在計數器計數到112 時,表示遍歷完成,輸出結果。該模塊優化的目的是降低本地SSS 的生成時延和計算時產生的處理時延,SSS 生成時延是利用查表解決的,每一個SSS 對應一張表,存儲著頻域127 點的數值,在使用時無需消耗額外時鐘周期進行生成。計算的處理時延通過分組遍歷進行優化,分組越多性能越接近并行計算,但消耗的硬件資源也就越多。

3.4 實驗結果分析

通過連接整機射頻后實際采樣,經過設計的FPGA模塊得到的是上板后的真實結果:小區ID 126 和499的信號。

上板測試的結果正確,功能正常,能正確解出小區ID,正確給出10 ms 幀頭,從而能確保傳輸給物理層準確信號,大大提高了解析速度。

4 結束語

本文介紹了5G NR 新一代通信的幀格式,并對5G NR 小區搜索算法進行了研究與仿真,并對PSS 與SSS 同步搜索的算法進行了FPGA 實現,經過仿真驗證和硬件實現驗證了正確性,確定了本研究的可行性。

參考文獻:

[1] 3GPP TS 38.201:NR;Physical Layer–General Description[S].

[2] 3GPP TS 38.215: NR; Physical layer measurements[S].

[3] 張越良.5G新空口下行同步和廣播信道的仿真與FPGA實現

[D].北京:北京郵電大學,2019.

[4] 郭秋陽.5G下行信號的同步與檢測技術研究[D].成都:成都電子科技大學,2019.

[5] 3GPP TS 38.214: NR; Physical layer procedures for data[S].

(本文來源于《電子產品世界》雜志社2021年5月期)

評論