“單正向”柵驅動IGBT簡化驅動電路

目前,為了防止高dV/dt應用于橋式電路中的IGBT時產生瞬時集電極電流,設計人員一般會設計柵特性是需要負偏置柵驅動的IGBT。然而提供負偏置增加了電路的復雜性,也很難使用高壓集成電路(HVIC)柵驅動器,因為這些IC是專為接地操作而設計──與控制電路相同。因此,研發有高dV/dt能力的IGBT以用于“單正向”柵驅動器便最為理想了。這樣的器件已經開發出來了。器件與負偏置柵驅動IGBT進行性能表現的比較測試,在高dV/dt條件下得出優越的測試結果。

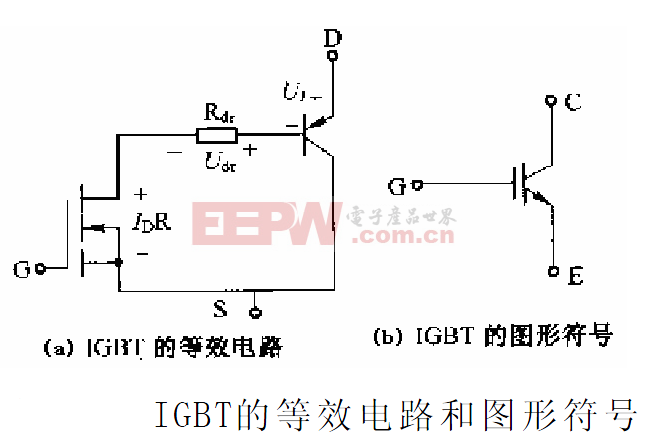

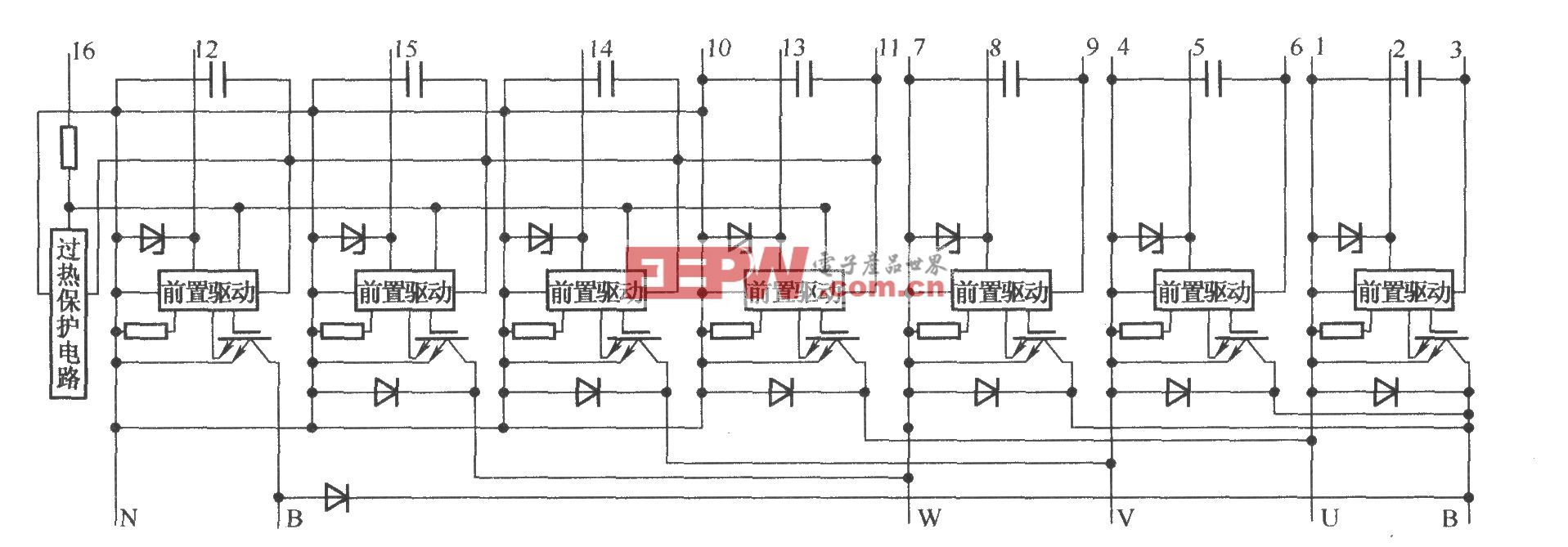

為了理解dV/dt感生開通現象,我們必須考慮跟IGBT結構有關的電容。圖1顯示了三個主要的IGBT寄生電容。集電極到發射極電容C,集電極到柵極電容C和柵極到發射極電容CGE。

這些電容對橋式變換器設計是非常重要的,大部份的IGBT數據表中都給出這些參數:

輸出電容,COES=CCE+CGC(CGE短路)

輸入電容,CIES=CGC+CGE(CCE短路)

反向傳輸電容,CRES=CGC

圖2給出了用于多數變換器設計中的典型半橋電路。集電極到柵極電容C和柵極到發射極電容C組成了動態分壓器。當高端IGBT(Q2)開通時,低端IGBT(Q1)的發射極上的dV/dt會在其柵極上產生正電壓脈沖。對于任何IGBT,脈沖的幅值與柵驅動電路阻抗和dV/dt的實際數值有直接關系。IGBT本身的設計對減小C和C的比例非常重要,它可因此減小dV/dt感生電壓幅值。

如果dV/dt感生電壓峰值超過IGBT的閥值,Q1產生集電極電流并產生很大的損耗,因為此時集電極到發射極的電壓很高。

為了減小dV/dt感生電流和防止器件開通,可采取以下措施:

關斷時采用柵極負偏置,可防止電壓峰值超過V,但問題是驅動電路會更復雜。

減小IGBT的CGC寄生電容和多晶硅電阻Rg’。

減小本征JFET的影響

圖3給出了為反向偏置關斷而設計的典型IGBT電容曲線。CRES曲線(及其他曲線)表明一個特性,電容一直保持在較高水平,直到V接近15V,然后才下降到較低值。如果減小或消除這種“高原”(plateau) 特性,C的實際值就可以進一步減小。

這種現象是由IGBT內部的本征JFET引起的。如果JFET的影響可以最小化,C和C可隨著VCE的提高而很快下降。這可能減小實際的CRES,即減小dV/dt感生開通對IGBT的影響。

IRGP30B120KD-E是一個備較小C和經改良JFET的典型IGBT。這是一個1200V,30A NPT IGBT。它是一個Co-Pack器件,與一個反并聯超快軟恢復二極管共同配置于TO-247封裝。

設計人員可減小多晶體柵極寬度,降低本征JFET的影響,和使用元胞設計幾何圖形,從而達到以上的目標。

對兩種1200V NPT IGBT進行比較:一種是其他公司的需負偏置關斷的器件,一種是IR公司的NPT單正向柵驅動IRGP30B120KD-E。測試結果表明其他公司的器件在源電阻為56Ω下驅動時,dV/dt感生電流很大。

比較寄生電容的數據,IR器件的三種電容也有減小:

輸入電容,CIES減小25%

輸出電容,COES減小35%

反向傳輸電容,CRES減小68%

@V=0V

CS (pF)

CS (pF)

CS (pF)

負偏置柵驅動IGBT

4000

1400

1100

IRGP30B120KD-E

3000

900

350

圖5顯示出IR器件的減小電容與V的關系,得出的平滑曲線是由于減小了JFET的影響。當V=0V時,負偏置柵驅動器件的C為1100pF,IRGP30B120KD-E只有350pF,當VCE=30V時,負偏置柵驅動器件的C為170pF,IRGP30B120KD-E的CRES為78pF。很明顯,IRGP30B120KD-E具有非常低的C,因此在相同的dV/dt條件下dV/dt感生電流將非常小。

測試條件:

電壓率,dV/dt=3.0V/nsec

直流電壓,Vbus=600V

外部柵到發射極電阻Rg=56Ω

環境溫度,TA=125

評論