DS-SS接收機全數字AGC的FPGA實現

考慮到噪聲的影響,將新的計數值與正常計數值之間的差值送入低通濾波器進行濾波。低通濾波器的離散方程為:

y(n)=α·y(n-1)+(1-α)·x(n) (7)

其中,x(n)為低通濾波器的輸入,y(n)為低通濾波器的輸出,α為濾波器系數。

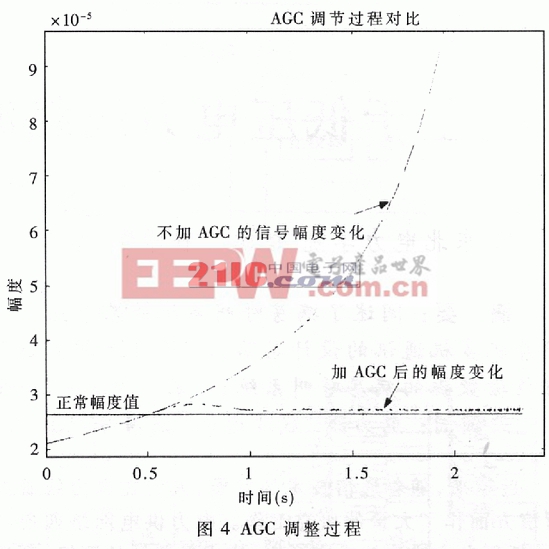

外部AGC控制模塊中的增益ψ用來控制AGC調整速度。ψ越大,調整速度越快,但會導致整個環路過沖和振蕩,并導致輸入信號有寄生調幅;ψ越小,調整速度越慢,但好處是不會過沖,并在一定程度上避免了寄生調幅。

相關推薦

-

herbertwj | 2004-08-15

-

-

-

sandman555 | 2005-02-05

-

-

-

-

-

-

sandman555 | 2005-02-05

-

-

-

sandman555 | 2005-02-05

-

xiaohua | 2002-09-24

-

評論