DS-SS接收機全數字AGC的FPGA實現

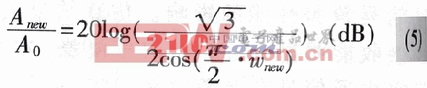

因此中頻輸出信號幅度與正常信號幅度的比值為:

由(5)式可以看出,中頻輸出連續信號幅度相對于正常信號幅度的比值與MAG端輸出信號的占空比有關,因此AGC控制模塊的關鍵是設計一個電路來檢測輸出信號的占空比。

利用一個計數器,采用射頻前采樣時鐘16.368MHz作為計數時鐘,在MAG高電平時計數。如果取計數時間為kms,則信號幅度處于射頻前端動態范圍之內時,正常的計數值為(k×10 -3×16.368×10 6)/3,記為n0。設接收信號幅度變大時,計數器的新計數值為n,則可推算出新的占空比為

wnew=n/3n0 (6)

由(5)和(6)式可知,已知新計數值和正常計數值就可計算出占空比,從而可計算出新的輸入信號幅度與正常信號幅度的比值或對應分貝值。中頻連續信號輸出幅度相對于正常幅度的放大dB值正是AGC控制模塊要輸出給數控衰減器的數值,因此衰減值dB轉換表就是基于(5)和(6)式構建的。要注意數控衰減器的衰減量并不是連續可調的。AT90-0106數字衰減器的衰減分辨率為1dB,最高衰減器為50dB.因此整個轉換表也是以1dB為最小單位,將計數值(反映占空比)映射到衰減dB值。

評論