SuVolta成功獲得1060萬美元風險投資

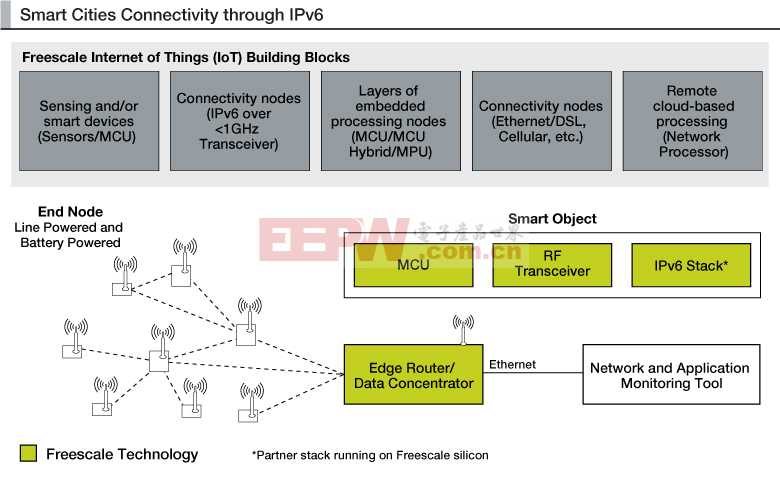

2014年1月15日,致力于為低功耗、高性能的集成電路芯片開發(fā)可擴展式半導體技術的SuVolta公司宣布其已獲得1060萬美元的資金。新投資商Fujitsu Semiconductor Limited加入了現(xiàn)有投資商Kleiner Perkins Caufield & Byers (KPCB)、August Capital、New Enterprise Associates(NEA)、 Northgate Capital 以及DAG Ventures的行列參與了這輪融資。SuVolta將把所得資金用于加快其低功耗芯片技術在半導體集成電路的設計和制造中的使用,滿足物聯(lián)網(wǎng)、DRAM以及移動計算等超低功耗應用的需求。

本文引用地址:http://www.j9360.com/article/215612.htm“我們正在走向一個日益‘互聯(lián)’的世界,降低功耗和控制成本已成為半導體行業(yè)的最大挑戰(zhàn),”SuVolta 董事會成員、NEA 普通合伙人Forest Baskett 如是說。“為了解決這些挑戰(zhàn),SuVolta對業(yè)界最經(jīng)濟有效的工藝技術 - 平面(planar bulk)CMOS 工藝進行了有效改良,而這對新興的物聯(lián)網(wǎng)市場的發(fā)展至關重要。”

“Fujitsu Semiconductor 致力于為消費類和移動市場開發(fā)高效、節(jié)能的產(chǎn)品,”Fujitsu Semiconductor Limited公司高級執(zhí)行副總裁Haruyoshi Yagi說道。“我們對SuVolta的投資體現(xiàn)了兩家公司之間良好的合作關系,以及我們對于DDC(Deeply Depleted Channel)技術在各個半導體工藝節(jié)點上取得廣泛應用的信心。”

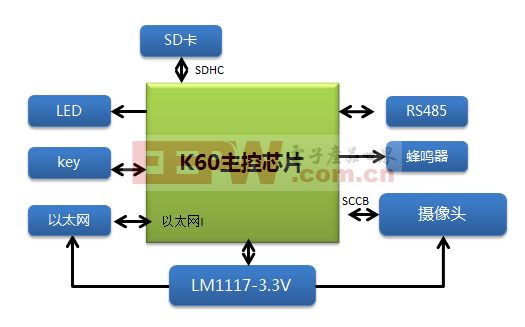

SuVolta公司開發(fā)并授權的晶體管工藝和設計技術可大大提高集成電路的功耗效率和性能。由于SuVolta的技術采用平面CMOS工藝,對于從90nm到20nm的基于CMOS的邏輯集成電路以及DRAM集成電路均可提供顯著的功耗和性能改善。DDC技術為集成電路設計者在多種產(chǎn)品的開發(fā)中提供了降低功耗的靈活性,這些IC產(chǎn)品包括對于當今的移動系統(tǒng)至關重要的處理器、存儲器和SOC。

“這一新的投資顯示了人們對于我們技術的熱情,以及對我們的技術能在DRAM、物聯(lián)網(wǎng)和移動計算等大規(guī)模市場中發(fā)揮功用的信心,” SuVolta 總裁兼首席執(zhí)行官Bruce McWilliams 說道。“DDC技術現(xiàn)已量產(chǎn),許多業(yè)界頂級的晶片代工廠和半導體公司都對通過超低功耗優(yōu)化來獲得競爭優(yōu)勢顯示出日益增長的興趣。”

物聯(lián)網(wǎng)相關文章:物聯(lián)網(wǎng)是什么

評論