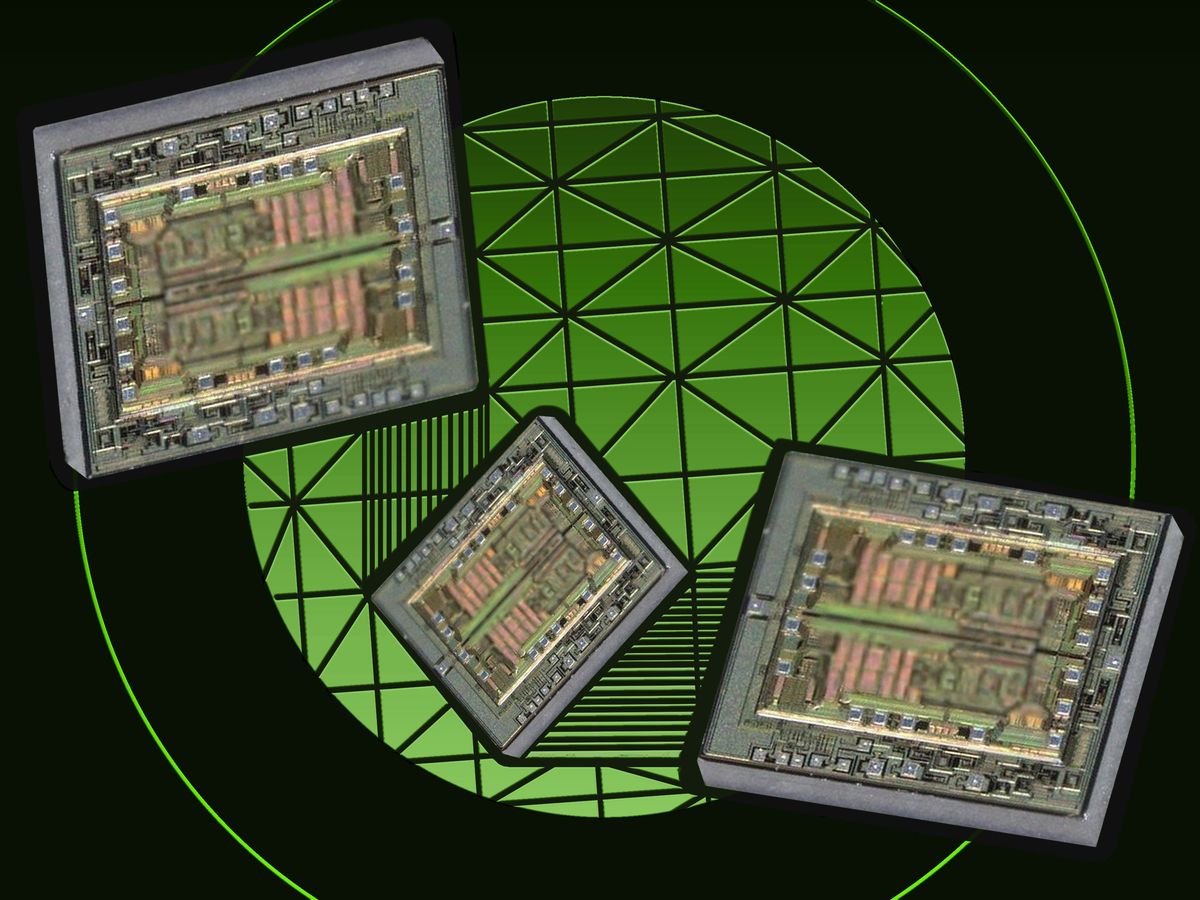

薄膜3D模擬IC:堆疊式 IC 可在更小尺寸中降低成本并提高性能

盡管數字技術不斷進步到商業、工業和休閑活動的各個領域,但模擬集成電路 (IC) 在全球半導體市場上仍占有一席之地。今年,收入預計將達到 850 億美元,相當于 10% 的年復合增長率。推動這一需求的是人工智能、物聯網技術和自動駕駛汽車的進步,所有這些都依賴于模擬 IC 來實現傳感和電源管理等功能。與僅處理二進制信號的數字 IC 不同,模擬 IC 可以處理溫度和聲音等連續信號,因此它們對于與物理環境連接至關重要。

本文引用地址:http://www.j9360.com/article/202503/467747.htm著眼于這一不斷擴大的市場,兩家總部位于東京的公司 Oki Electric Industry Co. 和 Nisshinbo Micro Devices 合作開發薄膜模擬 IC。這些 IC 還可以垂直堆疊,兩家公司聲稱這提高了電子產品小型化和一次集成更多 IC 的努力。 該技術還通過在更小的空間內實現更多功能或提高性能來降低成本并增加功能。

“我們生活在一個由聲音、光線、溫度和壓力組成的模擬世界,”Nisshinbo 生產工程助理經理 Toshihiro Ogata 說。模擬 IC 將物理世界和數字世界連接起來,處理連續的物理信號,例如自動駕駛汽車中的攝像頭和激光雷達檢測到的光線和距離,并將其轉換為數字數據以支持安全駕駛。

薄膜 3D 模擬 IC 開發

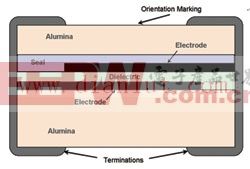

薄膜 3D 模擬 IC 的開發涉及OKI 的晶體薄膜鍵合 (CFB) 工藝,該工藝將模擬 IC 的功能薄膜層從襯底上剝離出來。(具體過程是商業機密。然后將分離的層粘合到另一個由絕緣層(如氧化硅)隔開的模擬薄膜層上。鍵合是通過分子之間的吸引力完成的,這種現象稱為分子間鍵合。傳統的引線鍵合以電氣方式連接堆疊層。

“與我們的 CFB 堆疊相比,標準堆疊工藝通常使用 TSV [通過硅通孔,一種連接堆疊芯片的垂直布線方法],并涉及先進的加工和特殊設備,”沖電氣 CFB 開發部總經理 Kenichi Tanigawa 說。他說,使用 TSV 連接的堆棧中單個芯片的厚度從幾十微米到幾百微米不等。“然而,在 CFB 堆棧中,每個芯片的厚度只有 5 到 10 [微米],這就是為什么可以在廣泛使用的遺留系統上使用低成本的傳統半導體光刻技術重新布線的原因。”

CFB 堆疊還支持使用多種不同的 3D 集成方法。一個簡單而聰明的工藝使用相同的 IC 設計,其中布線焊盤沿一個邊緣排列。在第一層鋪設完畢后,每個后續 IC 層的尺寸略微減小并旋轉 90 度,使前一層的焊盤暴露在外。這種方法可用于連接多達四層 IC。

然而,由于堆疊模擬 IC 非常薄,層之間會發生串擾,這可能會導致 IC 的信號干擾、噪聲和性能下降。這就是 Nisshinbo 憑借其專有屏蔽技術介入的地方。

“我們使用鋁作為使用傳統半導體工藝鋪設的屏蔽材料,”Nisshinbo 的 Ogata 說。他解釋說,如果電路層的整個區域都被屏蔽,“它會產生一個大的寄生電容”,指的是電路層之間發生的不必要的電荷存儲,這可能會干擾電路運行。“這是因為,與工作電壓低于 5 伏的數字 IC 不同,模擬 IC 可處理高達 20 或 30 伏的電壓,這會增加寄生電容。”

為了防止這種情況,屏蔽僅適用于堆疊芯片之間發生干擾的關鍵區域,這些區域是 Nisshinbo 根據其數十年對模擬 IC 的研究和工作確定的。Ogata 說,這種定位減少了信號干擾,而不會影響電路功能。

Chiplet 集成的優勢

兩家公司指出,薄膜 3D 模擬 IC 堆疊也可用于模擬和數字 IC 組合的情況。這將使它們能夠用于小芯片,即可以組合以創建更復雜的器件的模塊化 IC。

“與大型單片器件相比,小芯片具有幾個優勢,”Ogata 說。不是將所有功能都塞進一個大芯片中,而是單獨處理傳感、處理和電源管理等不同功能。每個小芯片都可以針對其特定功能進行優化,從而降低成本。堆疊小芯片還降低了空間要求,從而實現了更小的器件。而且制造產量可能會更高,因為如果一個小芯片出現缺陷,則可以在組裝之前識別并更換小芯片。(而一個大芯片的缺陷意味著必須丟棄整個芯片。

盡管如此,在這種先進的集成成為現實之前,這些公司可能會面臨一些挑戰。

“小芯片方法對于下一代半導體制造非常重要,”蒙特利爾麥吉爾大學計算機和電氣工程教授 Gordon Roberts 說。雖然今天的小芯片已經允許某些組件(如 CPU、GPU 和內存)混合和匹配,但半導體發展的下一步將看到更多樣化的組件,如模擬、電源和光學芯片,使用創新的堆疊和互連技術無縫集成。

“能夠使用一種可以廉價地組裝混合組件袋的工藝將是朝著正確方向邁出的一步,”Roberts 說。“然而,由于該工藝使用減薄的半導體器件堆疊在公共襯底上,因此減薄步驟會引入制造缺陷。”除了威脅制造良率外,裂紋等缺陷還可能在測試過程中滑落,從而導致可靠性問題。“因此,需要確定公司如何處理單個模具并將它們打包在一起,”Roberts 說。

沖電氣 (OKI) 和日清紡 (Nisshinbo) 相信他們可以克服這些問題,并且已經計劃將他們的新方法用于商業應用。

“將我們的技術應用于小芯片技術意味著我們將能夠提供一系列不同的模擬 IC”,OKI 的 Tanigawa 說。“各種數字、模擬、光學和其他半導體器件的異構集成將有助于引領未來新型半導體芯片的開發。”他補充說,兩家公司已經開始基于他們的技術開發新產品,并計劃到 2026 年實現大規模生產。

評論