KeyStone存儲器架構

序言

隨著全球范圍內的海量數據對無線和有線網絡的強大沖擊,運營商面臨著嚴峻的挑戰,他們需要不斷推出既能滿足當前需求也能滿足未來需求的網絡。因此,通信基礎局端設備制造商在致力于降低每比特成本和功耗的同時,也在不斷尋求能夠滿足當前及至未來需求的核心技術。TI最新推出的新型 KeyStone 多內核 SoC 架構能夠游刃有余地滿足這些挑戰。

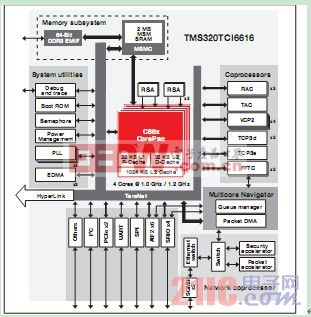

基于新型 KeyStone 多內核 SoC 架構的器件集成了多達 8 個TMS320C66x DSP CorePac,能夠實現無與倫比的定點與浮點處理能力。KeyStone 架構經精心設計,是一款效率極高的多內核存儲器架構,允許并行執行任務的同時,還能使所有的 CorePac實現全速處理。本文探討了 KeyStone 存儲器的層級結構,及其將如何與 SoC架構的其他組件進行連接以實現多內核全速處理。

德州儀器 (TI) 積極創新,努力迎接多內核 SoC 技術帶來的挑戰。TI KeyStone 架構擁有眾多組件,其中包含全新的 C66x 定點和浮點 DSP 內核、可實現基于標準的優化功能和接口的可配置協處理器、層級存儲器架構、TeraNet 交換結構以及可將上述各組件連結在一起的多內核導航器。KeyStone 架構具備三個存儲等級。每個 C66xCorePac 均擁有自己的一級程序 (L1P) 和一級數據 (L1D) 存儲器。另外,每個 CorePac 還擁有局域的二級統一存儲器。每個局域存儲器均能獨立配置成存儲器映射的SRAM、高速緩存,或是兩者的組合。

KeyStone 架構包含共享的存儲器子系統,其由通過多內核共享存儲器控制器 (MSMC) 連接的內部和外部存儲器組成。MSMC 允許CorePac動態地分享程序和數據的內外部存儲器。

圖 1 - KeyStone 器件方框圖 - TMS320TCI6616

2

MSMC 的內部 RAM 允許各部分被配置成共享的二級 RAM 或者共享三級 (SL3) RAM,從而可為程序員提供高度的靈活性。SL2 RAM 僅能夠在局域 L1P 和 L1D 高速緩存中緩存,而 SL3另外還可在局域 L2 高速緩存中進行緩存。

為向軟件執行提供快速通道,外部存儲器同內部共享存儲器一樣,通過同一存儲器控制器進行連接,而并非像在嵌入式處理器架構上所進行的傳統做法那樣,與芯片系統實現互通互連。外部存儲器始終被看作是 SL3 存儲器,并可在 L1 和 L2 中緩存。接下來的我們將探討在KeyStone 架構中實現的各種性能增強。

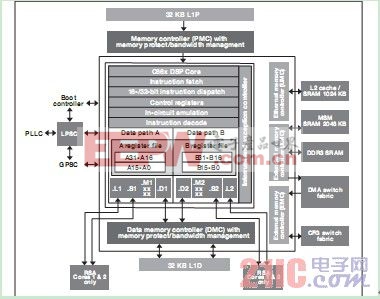

存儲性能增強C66x CorePac 的內部存儲器架構與此前 C6000™ DSP 系列產品相比,主要在四個方面實現了增強,而這突出體現在性能指標和實用性方面。這些改進旨在實現如下優勢:1) 無論多個內核和數據 I/O 是否處于高度繁忙狀態,都能提高存儲器各級的執行效率;2) 更輕松便捷地管理多個內核和數據 I/O 之間的緩存一致性;3) 存儲器的保護與地址擴展,以及;4) 將對軟錯誤的保護進一步擴展至較高級別的存儲器。

執行效率 —— C66x CorePac 的存儲器子系統在功能上與最新的 C64x+™ 和C67x™ 系列 DSP 系列 C64x+™ 和 C67x™ 的相當。每個局域 L1存儲器均為 32KB,并能夠配置成全速緩存(默認)、全存儲器映射 SRAM,或是 4、8 或 16KB 高速緩存選項的組合。L1P 始終為直接映射,而 L1D 則始終為雙向集關聯 (two-way set-associative)。

圖2 – CorePac 存儲器增強

評論