助力RISC-V處理器用于邊緣AI,Codasip提供EDA工具集和IP

1 關注的嵌入式AI市場

機器學習算法給我們的生活帶來的益處是前所未有的。我們看到越來越多的智能應用正在靠近邊緣,并集成到各種類型的產品中。

胡征宇(Codasip大中華區(qū)總經理)

隨著對高性能處理器的需求不斷增長,摩爾定律等半導體縮放定律繼續(xù)顯示出其局限性,對處理器優(yōu)化的需求不可避免;RISC-V 的設計就是為了實現(xiàn)這一種優(yōu)化的演進模式。然而,沒有放之四海而皆準的處理器優(yōu)化方法:由于每個工作負載和應用都有自己的需求,實際上存在不同的優(yōu)化方法。您可以在不同層面修改處理器IP,而每個層面都有自己特有的價值和優(yōu)點。通過為RISC-V 處理器提供定制功能,更大范圍的算法可以在邊緣得到實現(xiàn)。

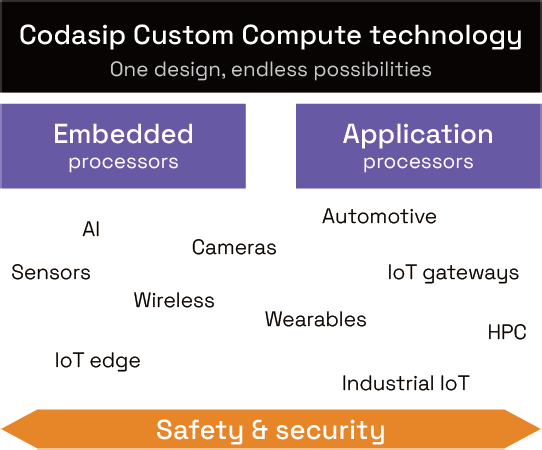

Codasip 是一家專門幫助開發(fā)人員使其產品實現(xiàn)差異化的處理器解決方案公司。我們通過結合開放的RISC-V ISA、Codasip Studio 處理器設計自動化工具集和高質量的處理器IP 來提供定制計算。

2 工程師遇到的開發(fā)挑戰(zhàn)

開發(fā)人員主要面臨與機器學習算法所需計算要求相關的挑戰(zhàn)。這些要求可能總體量很大,并且在小型邊緣計算上實現(xiàn)此類算法的實際情況中,它們可能因受到限制而成為更小、更簡單的模型。但是,可以通過將定制化引入到給定模型中,來解決小型處理器可能必須要去處理的問題。這種定制化功能可以實現(xiàn)更快的模型推理、更低的功耗和更高的應用性能。

在Codasip,我們不認為存在一種固定和絕對的性能、功耗和芯片面積(PPA)指標衡量標準。重要的是我們的客戶在其最終芯片中獲得的最終PPA 指標,因此使用相同IP 的不同客戶得到的PPA 則很可能大不相同。無需花費大量時間手動調整IP,您可以使用我們的工具來定制IP,以獲得比市場上任何產品都更好的PPA。而且,當您在同一個SoC 中使用多個處理器時,您可以決定對每個處理器進行不同的優(yōu)化,以確保獲得最大效率。

3 Codasip的解決方案

借助我們的工具鏈Codasip Studio,我們可提供處理器設計自動化工具。客戶可以從我們的任何一個基準性IP 內核開始,然后做出最佳的軟件和硬件權衡,并實現(xiàn)最優(yōu)功能和PPA。

我們的L31 內核是一款低功耗、通用型的嵌入式RISC-V CPU,在人工智能邊緣設備中很受歡迎。我們最近還推出了A730 內核,這是一款多功能的中端64 位應用內核,能夠運行Linux 和RTOS,非常適合在功率受限的設備上執(zhí)行復雜的計算任務。A730 內核經過高度優(yōu)化,具有更大的靈活性。它可以通過控制以下幾個選項來適應特定的用例,包括:

● 內核數(shù)量:1~4 個

● 具有可定制內存映射的內存保護

● 分支預測

● 指令和數(shù)據緩存大小

● 共享L2 緩存大小和結合性

● 轉譯后備緩沖器(TLB)

(本文來源于《EEPW》2023年11月期)

評論