工程師20年經驗總結:ASIC芯片的成本計算

大規模集成電路芯片, 比如SoC(System on chip),由多核CPU和GPU組成,用于智能手機主芯片、車載多媒體和導航系統,或者特定用途的集成電路芯片ASIC(Application specified integrated circuit),用于電子控制模塊的信號處理,算法運行和控制執行部件, 比如自動泊車、啟動安全氣囊、自動駕駛的雷達信號分析等。這些芯片是未來數字化、智能化的核心元件。但是,它們的成本是怎樣構成? 客戶所能知道的就是半導體公司或芯片貿易商(Distributor)的報價。特定用途集成電路ASIC芯片的成本構成對絕大多數用戶來說更是一無所知。作者通過20多年來積累的成本工程經驗和對集成電路芯片制造工藝過程的系統分析, 開辟了一條對集成電路芯片進行成本分析和成本計算的路徑。

本文引用地址:http://www.j9360.com/article/201804/378125.htm

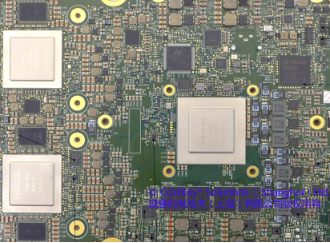

圖1 某電動汽車車載服務器的SoC和ASIC

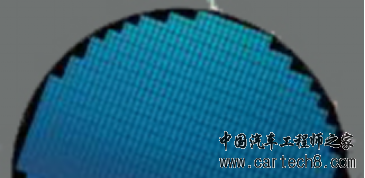

集成電路芯片的制造分為兩部分,第一部分是前端工藝(Frontend),是把晶片毛坯通過一步一步復雜的工序,制作成有半導體結構化的晶片(見圖2)。

圖2 半導體結構化的晶片

每一個晶片上可以制作出幾千甚至幾萬個集成電路的裸片(Die),每一個裸片,就是一個芯片的初始狀態。在第二部分后端工藝(Backend),把這一個個裸片分離出來,連接到外面(bonding),然后用注塑封裝,就制作出一個個集成電路芯片了(見圖3)

圖3 封裝好的集成電路芯片

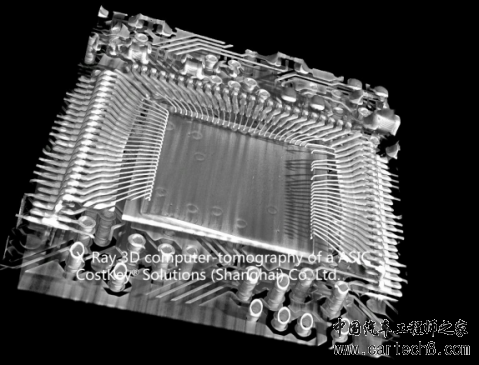

為了能更好的觀察封裝好的集成電路芯片,通過倫琴射線的3D計算機成像CT(Computer-tomography), 可以清晰地看到集成電路芯片的裸片尺寸,外連線的結構等。

圖4 特定用途集成電路芯片(ASIC)在倫琴射線下的3D計算機成像

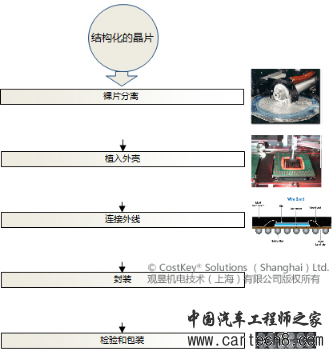

集成電路芯片的前端工藝和后端工藝見圖5和圖6描述。

圖5 集成電路前端工藝的例子 (n-通道場感應三極管)

圖6 集成電路的后端工藝

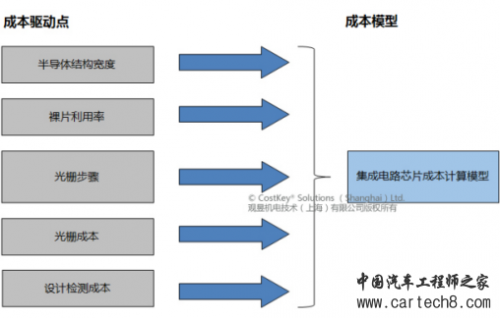

通過對集成電路前端及后端工藝的系統分析,得出如下的主要成本驅動點及成本模型:

圖7 集成電路芯片的成本驅動點和成本計算模型

以一個自動變速箱電子控制模塊中的特定用途集成電路芯片(ASIC)為例,依據以上的成本模型,計算出這個芯片的成本:

前端成本 1.56 歐元

后端成本 0.31 歐元

芯片成本 1.87 歐元

總結

未來的汽車工業,在數字化、自動駕駛、新能源車型的需求下,越來越多的集成電路芯片,比如SoC或者ASIC投入實際應用,無論是主機廠還是系統供應商,都很想知道它們的成本構成,使用觀昱機電技術(上海)有限公司的集成電路芯片成本計算模型,可以準確地計算出集成電路芯片的成本。

評論