基于FPGA+ARM的HDLC協議控制器的設計與實現

摘要:針對飛控模擬裝置中基于HDLC協議通信需求,完成了一種新的基于FPGA+ARM架構HDLC協議控制器的設計。文中首先介B了HDLC協議的幀結構和循環冗余校驗(CRC)原理,然后結合FPGA可進行任意數據寬度操作和ARM編程簡單靈活的優點,有效實現了符合HDLC協議的幀結構和CRC校驗的應用方法,滿足HDLC協議要求。應用結果表明設計能夠很好地滿足各項功能指標的技術要求。

本文引用地址:http://www.j9360.com/article/201610/308490.htm高級數據鏈路控制(HDLC,High-Level Data Control)是一種同步數據傳輸、面向比特的數據鏈路層協議,具有差錯檢測功能強大、高效和同步傳輸的特點,目前HDLC協議已成為是通信領域中應用最廣泛的協議之一,在飛行器設計領域經常用作飛控與舵機,助推器等之間通信的通信協議。

飛行控制模擬裝置是在飛行器研制的方案階段,用于飛行控制系統軟件開發及仿真評估,飛行控制軟件往往是A級軟件,它的任何問題都將造成飛行失效,進而引起整個系統的癱瘓。采取飛行器控制系統模擬裝置進行軟件算法驗證,對各個分系統軟件調試和系統驗證,能夠加快飛行器設計進度,減少設計風險和成本。

本文研究的HDLC協議控制器用于某型飛行器的飛控模擬裝置與舵機控制器之間的通信。一般而言HDLC協議主要是通過使用專用芯片和軟件編程的方式來實現。目前在市場上有很多專用的HDLC協議處理芯片如MT8952B、MK5025,這些芯片性能可靠但功能針對性太強,適合應用于特定用途的大批量產品中。軟件編程方式是通過針對微控制器或信號處理器進行編程,但是由于微控制器或信號處理器是基于字節(8位、16位等)的處理,而HDLC協議幀的解析和生成是面向比特的處理,因而這種方法會大大增加微處理器或信號處理器的負荷。考慮到本設計中針對的飛控模擬裝置中存在大量不同總線接口需要處理,其處理器為FPGA+ARM,FPGA能對任意數據寬度的信號進行處理,ARM具備編程簡單,修改靈活的優點,為此本文在此基礎上采用FPGA+AHM的方式利用FPGA完成符合HDLC協議的數據傳輸控制,ARM完成CRC校驗和信息幀解包,最終實現HDLC協議控制器的設計。

1 HDLC協議及CRC原理介紹

HDLC是高級鏈路層控制協議,面向位的數據鏈路層協議。HDLC通常為點一點或點一多點結構,可用于半雙工或全雙工通信,采用同步傳輸方式,常用于中高速數據傳輸場合。HDLC采用滑動窗口協議,可以同時確認幾個幀;另外,每個幀都含有地址地段,這樣在多點結構中,主站可以同時和多個從站建立連接,而每個從站只接收含有本站地址的幀,因此HDLC的傳輸效率比較高,具有較高的吞吐率。在HDLC協議控制器中,其實現的關鍵在于兩個方面,一方面為保證幀間隔標志的唯一性,在后續的字段中采用“0”比特插入/刪除技術。發送時,幀間隔標志之外的所有信息,只要出現連續的5個“1”,則自動插入一個“0”;同樣,接收方在接收數據時,只要遇到連續的5個“1”,則自動將其后的“0”刪除掉;另一方面是CRC碼的產生及校驗,即在發送端,利用生成多項式自動生成一幀數據的CRC校驗碼并附在信息段后發送出去;在接收端,對接受到的一幀數據作CRC碼的校驗。

CRC的全稱為Cvclic Redundancy Chcck,中文名稱為循環冗余校驗。它是一類重要的線性分組碼。編碼和解碼方法簡單,檢錯和糾錯能力強,在通信領域廣泛地用于實現差錯控制。其基本原理是:對于一個給定的(N,K)碼(在K位信息碼后再拼接R位的校驗碼,N=R+K),可以證明存在一個最高次冪為N-K=R的多項式C(x)。根據C(x)可以生成K位信息的校驗碼,而G(x)叫做這個CRC碼的生成多項式。校驗碼的具體生成過程為:假設要發送的信息用多項式C(X)表示,將C(x)左移R位(可表示成C(x)*2R),這樣C(x)的右邊就會空出R位,這就是校驗碼的位置。用C(x)*2R除以生成多項式G(x)得到的余數就是校驗碼。根據R的不同,形成多種不同的CRC標準,如(3RC-4:x4+x+1、CRC-8:x8+x6+X4+x3+X2+ X1、CRC16-CCITT:x16+X12+x5+1等。本文采用的即是CRC16-CCITT標準。

2 HDLC控制器設計

2.1 HDLC協議處理電路設計

為滿足飛行器設計驗證需求,可以實現基于HDLC協議傳輸的靈活配置,其功能和技術指標要求如下:422全雙工;傳輸速率可調,最大達到2 Mbps;通信距離不超過5 m;通訊誤碼率小于10-7;幀頭7E與幀尾個數可調,CRC校驗方式采用CCITT-CRC16。根據功能和技術指標要求以及飛控模擬裝置總體配置狀況,控制器總體框圖如圖1所示。

其中數據處理單元采用ARM實現,完成數據幀的CRC校驗和信息提取,并根據設定初始化傳輸控制單元的參數,包括波特率,7E有效個數;傳輸控制單元采用FPCA實現,主要功能是實現HDLC傳輸控制邏輯和數據緩存;接口總線采用全雙工RS422數據總線,由于RS422傳輸線為差分電壓,因此需要進行電平轉化,為此根據設計要求本文設計的控制器選用MAX3491作為電子轉換芯片,其轉換速度達到10Mbps以滿足需要。文中將針對HDLC控制器設計重點介紹數據處理單元、輸出控制邏輯兩部分。

2.2 HDLC傳輸控制單元

HDLC傳輸是按位操作,因此采用FPGA完成,FPGA采用altera公司的CYCLONE Ⅱ系列的FPGA,開發平臺基于QuartuslI 6.0開發環境,利用有限狀態機設計實現HDLC協議的傳輸控制部分,并最終以IP核的方式給出設計實現,便于開發人員進行維護和升級。

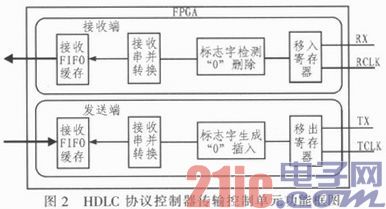

由于HDLC協議控制器是全雙工通信,即包含了HDLC同步比特數據的接收電路設計和HDLC同步比特數據幀的發送電路設計。在FPGA的設計中,接收端和發送端都是基于比特的處理,其功能框圖如圖2所示。

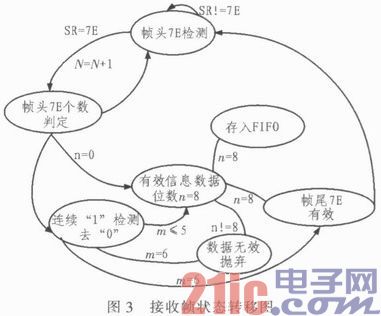

在接收端,一直根據接收時鐘RCLK信號的上升沿接收數據,在信息幀發出以前,判斷幀頭“7E”,并記錄“7E”個數,當“7E”個數滿足設定要求,開始啟動信息幀的接收,并開啟數1計數器,當遇到連續5個“1”時刪除其后的“0”,同時進行串并轉換,將數據按8BIT組成一字節,存入FIFO中,整字節接收完畢后,如接收到“7E”表明該信息幀結束,并開始記錄“7E”個數,當“7E”個數滿足幀尾設定要求,表明該幀接收完畢,否則表示接收出錯,拋棄該幀。圖3即為接收幀狀態轉移圖。

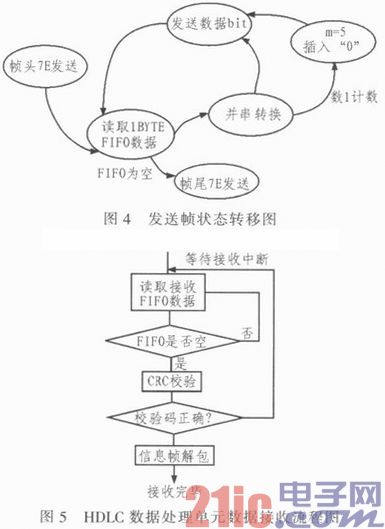

在發送端,接收到ARM啟動發送指令后,發送相應個數幀頭0x7E,然后將數據從發送FIFO中取出,進行并串轉換,在根據設置的時鐘TCLK的下降沿,逐位發送數據到Tx線路上,并且在連續發送了5個比特“1”后,自動插入比特“0”,發送結束后發送相應個數幀尾0x7E,結束該次發送。發送幀狀態轉移圖如圖4所示。

2.3 HDLC數據處理單元

HDLC數據處理單元主要完成信息的幀的CRC校驗和打包解包任務,其處理芯片采用意法半導體的STM32F103系列ARM芯片,該芯片具有開發簡單靈活,成本較低的優勢。數據處理單元對數據的處理同樣包括接收和發送兩部分,以接收為例,具體工作流程圖如圖5所示。

當進入接收中斷進程時,首先讀空接收FIFO,其中最后兩次讀出的數據為該幀信息的CRC校驗碼,利用該校驗碼進行CRC校驗,校驗采用CRC-16-CCITT標準,生成r取值為16,其生成多項式為:C(x)=x16+x12+x2+1傳統CRC校驗是對消息逐位處理,對于ARM來說,這樣效率是很低的。為了提高時間效率,通常的思想是以空間換時間。考慮到內循環只與當前的消息字節和crc_reg的低字節有關,針對crc_reg低字節建立數表進行查詢相應的CRC校驗碼,最終循環完畢如果沒有差錯發生則結果應為0。

發送單元與接收單元類似,為其逆過程,首先將信息按約定幀格式打包,然后進行CRC校驗,將校驗碼放入信息幀的最后2個字節,并將該信息幀通過數據總線存入FPGA的發送FIFO中,最后寫入發送標志字,啟動FPGA發送傳輸控制邏輯。

3 驗證及結果

為完成設計,首先采用ModelSim進行仿真驗證,如圖6所示通過激勵文件生成ARM與FPCA的讀寫時序,給出符合HDLC幀格式的一組數據寫入FPGA發送FIFO,并啟動發送,在激勵文件中將RX/RCLK與TX/TCLK短接,形成回環,FPGA根據協議控制器接收到數據,并將數據存入接收FIFO,完成驗證。其邏輯時序滿足HDLC協議幀格式和通信時序要求。

最后按照設計要求將設計好的HDLC通信協議控制器加載至FPGA與ARM上,并與串口通信卡BST23109進行回環測試,該卡能夠實現串口同步模式,通信滿足HDLC協議要求。試驗結果表明在5 m通信距離內,波特率可達2 Mb/s,誤碼率為10-8。

4 結論

文中針對飛行模擬裝置中HDLC協議的應用需求開展了HDLC協議控制器的設計,文中首先介紹了HDLC協議的相關內容,然后重點介紹了HDLC協議控制器軟硬件實現,詳細給出于HDLC協議控制器的沒計實現過程。通過仿真和實測試驗表明在5m通信距離內,波特率可達2Mb/s,誤碼率為10-8。在該飛行模擬裝置交付使用過程中,該控制器功能完整,能夠很好地滿足各項指標的技術要求。

評論