基于FPGA的高速數據傳輸研究

摘要:大數據發展如火如荼,解決串行數據高速傳輸已成當務之急。本文正是以此為出發點,介紹了Xilinx FPGA內嵌的高速串行收發器RocketIO。測試結果表明,RocketIO收發器的傳輸速度最高可達6.6Gbps,可以完全勝任各種高速數據的傳輸與處理。

本文引用地址:http://www.j9360.com/article/201608/296187.htm引言

近年來,電子行業的發展走進了黃金時期,優勢明顯的串行傳輸無論在速度上還是信號完整性上都得到了飛速發展。無論高速AD采樣后的數據接收,還是高速實時數據的傳輸與處理,都離不開高速串行總線。尤其對大型的采集系統,往往需要在單位時間里采集到成百上千個高精度的實時數據,這就要求在進行串行傳輸時速率達到百兆,甚至千兆每秒的級別。而Xilinx FPGA所提出的RocketIO 正是一種完全可以滿足當前需求的解決方案。

本文主要介紹了RocketIO GTX的原理,并在此基礎上提出設計中需要注意的設計要點,最后進行了板間高速數據傳輸的測試,給出了實時數據的采樣波形圖。

1 RocketIO GTX收發器介紹

RocketIO GTX是Xilinx公司FPGA內嵌的一種可配置的高速串行數據收發器,其傳輸速度在600Mbps~6.6Gbps[4]。該公司Virtex-5與Virtex-6系列FPGA都內嵌了RocketIO GTX,且其結構和工作原理也基本相同[1],本文將以Virtex-6 系列FPGA內嵌的GTX為重點進行介紹。

1.1 RocketIO GTX主要特點

● 每個通道收發器支持從600Mbps~6.6Gbps的全雙工傳輸速率;

● 收發器內嵌發送時鐘生成電路和接收時鐘恢復電路;

● 差分輸出端5級可配置電壓(110mV~1130mV);

● 發送端支持可編程預加重/去加重,和判定反饋均衡(DFE);

● 支持可編程差分輸出電壓擺幅(110mv~1130mv)和可編程預加重;

● 收發器支持直接和交流耦合方式,可兼容多種高速接口標準;

● 片內集成可編程差分終端電阻;

● 支持片內多種環回測試模式;

● PCS集成多種可選編碼功能,如comma字符對齊、8B/10B編碼、時鐘修正和通道綁定[2]。

1.2 RockerIO GTX內部結構

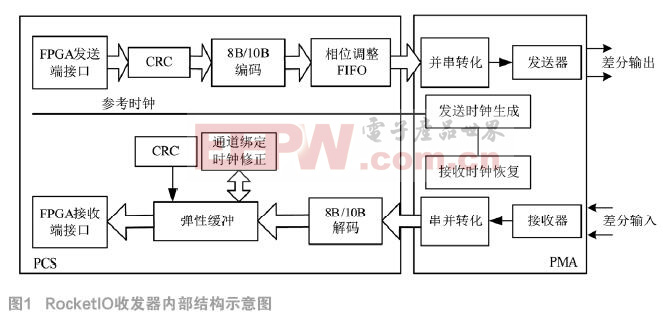

RocketIO GTX收發器由兩部分組成:PCS(Physical Coding Sublayer)和PMA(Physical Media Attachment,物理媒介層),如圖1所示。

其中 PMA部分主要包括串行和解串器、發送和接收驅動器、時鐘產生和恢復單元;PCS 部分主要包括 8B/10B 編解碼、通道綁定、時鐘修正和 CRC校驗模塊。

● 8B/10B 編解碼

8B/10B編碼機制是進行高速串行傳輸時普遍采用的編碼方式,其實現原理是將8位字符根據對應碼表轉化為10位字符,這種轉換保證了通道的直流平衡性,有利于交直流耦合,提高信道傳輸質量。

● 通道綁定

通道綁定(Channel Bonding),一種通過一定協議將多個串行通道綁定達到并行傳輸,目的在于實現對數據吞吐率增大的技術。綁定原理是,在所有并列的串行通道中,定義一個主通道,其它均為從通道,主通道發送同步使能信號來與其它從通道進行對齊,從而解決各個通道數據同步問題,實現串行通道的并行綁定。

● 串行器和解串器

在發送端,收發器把輸入GTX的參考時鐘作20倍頻,作為發送線路的參考時鐘,然后將經過編碼的并行數據轉化為串行數據,從串行差分端發送出去;在接收端,時鐘恢復電路從比特流中提取出時鐘相位和頻率,恢復出接收時鐘,將串行數據解碼并轉化為并行數據,送入用戶接口以進行其他操作。

● 時鐘修正

時鐘修正(Clock Correction)目的在于發送端與接收端的時鐘匹配,在收發器的TX端,對要發送的串行數據中插入特定的修正序列,RX端通過這些修正序列提供的信息對時鐘進行修正。

2 RocketIO GTX設計要點

要使RocketIO模塊以最佳性能工作,實際設計中需要考慮到諸多設計因素,本節將對設計中經常遇到的問題進行討論。

2.1 參考時鐘

高速串行數據的傳輸中,為了實現高速,對時鐘的要求當然就更為苛刻,這就要求用來驅動收發器的時鐘必須具備高性能、低抖動的特點。一般來講,GTX收發器提供了3種參考時鐘的驅動方式:

①從外部GTX專用時鐘端口輸入來驅動時鐘路由;

②從相鄰Quard的專用時鐘路由獲取;

③從FPGA內部獲取。

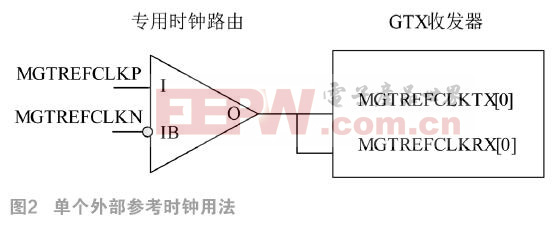

每個Quad中都擁有兩個專用差分時鐘輸入MGTREFCLK0[P/N]和MGTREFCLK1[P/N],它們是時鐘源的接口,為整個GTX的時鐘提供保障。在設計中,當選用這種方式的時鐘供應時,需要對原語IBUFDS_GTXE1進行例化。需將原語IBUFDS_GTXE1的輸出做為GTXE1的端口MGTREFCLKTX[0]和MGTREFCLKRX[0]的輸入。需要注意的是,即使在設計中未使用TX PLL,MGTREFCLKTX[0]仍然需要被連接[5]。單個外部參考時鐘用法如圖2所示。

前兩種參考時鐘的驅動方式都是使用GTX所集成的專用時鐘路由,在精度上能得到很好的保障。第三種由內部全局時鐘網絡提供,會引入更大的抖動,而且驅動能力也有限,因此要盡量避免使用。

2.2 用戶時鐘

GTX的接收端和發送端都有兩個用戶時鐘,這里以發送端為例進行介紹。這兩個時鐘分別為:TXUSRCLK和TXUSRCLK2。其中TXUSRCLK2是發送端TX的用戶時鐘,允許用戶直接使用,由GTX的內部時鐘TXOUTCLK驅動。用戶將并行數據傳輸到發送接口,在用戶時鐘上升沿被采樣并送入發送緩沖,經過編碼以及串行化之后發送出去。TXUSRCLK是PCS內部邏輯時鐘,不允許用戶直接使用,其大小取決于如下公式[3]:

![]()

由于在設計中通常會選擇8B/10B編碼,因此16bit并行數據經過編碼后變為20bit。這里需要注意的是,需要設置屬性GEN_TXUSRCLK=TRUE。此時,TXUSRCLK端口必須拉低,邏輯時鐘TXUSRCLK由GTX內部提供,并且用戶時鐘TXUSRCLK2大小與TXUSRCLK相同[4]。當設計中線速率選為3Gbps,可知用戶時鐘TXUSRCLK應為150MHz。時鐘結構如圖3所示。

GTX的接收端RX與TX基本相似,也包括兩個用戶時鐘分別為:RXUSRCLK和RXUSRCLK2。其中,RXUSRCLK2是GTX接收端的用戶時鐘,由恢復時鐘RXRECCLK驅動。RXUSRCLK的驅動方式和屬性設置與發送端一致[5]。

2.3 Comma 檢測對齊

Comma檢測對齊模塊是高速數據傳輸中必不可少的重要模塊,高速數據的識別對齊是傳輸中的核心問題。在RX接收模塊中,串行數據轉換為并行前,必須經過邊界字符對齊才能對所傳輸的數據進行識別,才能有后續的并行數據。在實現高速串行信號發送時,TX端會先發送comma字符,然后再發送數據。對應的RX接收端通過comma探測,當檢測到comma字符后,需要進行對齊,然后接收數據[6]。

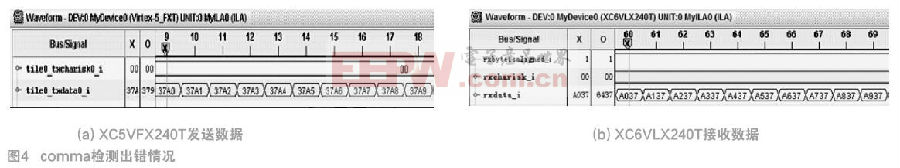

GTX收發器的comma模塊在實際解碼應用中通常選K28.1、K28.5和K28.7為comma字符,具體根據項目需求來選擇。設計中,為了確保數據的對齊,通常會選擇發送2000個左右的同步字符。在TX端發送K字符時,賦值TXCHARISK=2’b01,TXDATA=16’h43BC。這里TXCHARISK=2’b11表明對應數據的低字節為K字符,對應比特流中的comma字符。需要注意的是,當TXCHARISK=2’b11,發送TXDATA=16’hBCBC時,由于TXDATA中高八位和低八位相同,這樣在接收端容易出現錯位8位的情況。如圖4所示。

造成這種情況的原因是,在進行K字符探測對齊的過程中,將兩個K字符的低字節和下一個的高字節組合,這樣探測對齊系統會認為實現了對齊過程,在接下來的數據接收過程中會以這種方式進行對齊。

3 應用系統

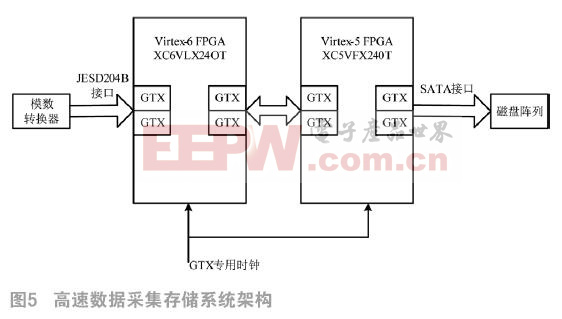

基于RcoketIO GTX的高速串行傳輸,設計出了一個高速數據采集存儲系統,采集端使用XC6VLX240T,存儲端使用XC5VFX240T。由圖5可以看出,ADC的高速數據是通過其自帶JESD204B接口與V6實現GTX互聯的,V6與V5兩FPGA間的數據傳輸也采用GTX傳輸,后面SATA設計中還是使用GTX來實現的。

從數據流來看,AD將采集的高速數據通過GTX(配置成JESD204B接口)送入Virtex-6,經過一定的數據處理后通過GTX發送至Virtex-5 FPGA,最終通過GTX(配置成SATA接口)存入磁盤陣列。由此可見,RocketIO GTX是整個系統中高速數據傳輸的核心。

4 實驗結果和分析

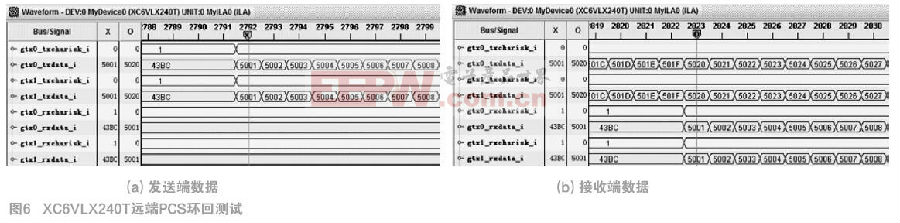

通常對系統設計中GTX通路的連接需要進行測試,以下將通過本V6端的PCS遠端測試來驗證其工作性能,也就是V6端發送測試數據至V5然后通過PCS環回至V6接收端,來看數據的正確與否。chipscope采樣如圖6所示。

由于遠端PCS環回模式可以同時測試兩端GTX的通信情況,故由圖6可知,XC6VLX240T、XC5VFX240T可以正常通信。

高速數據傳輸中,經常要對數據進行各種轉換,而數據的拼接與拆分是最常用的手段,圖7是對一路 0000-FFFF的遞增碼,將遞增碼拆分成兩路分別為4K數據和43BC。也就是將一個遞增碼分成TRIG1和TRIG2的兩路GTX數據進行發送來測試數據的正確性。

由數據總線圖可以看出,兩路數據成完美遞增狀態。

5 結束語

本文以高速數據傳輸為出發點,介紹了基于RocketIO GTX 的解決方案,并給出了以GTX為核心的應用系統設計。由此可見,采用 RocketIO收發器進行高速串行數據的傳輸,在保證速度的前提下,傳輸過程中的信號完整性也得到了極大的保障,為高速數據的傳輸提供速度和質量上的保證 。

參考文獻:

[1]Xilinx. Virtex-6 Family Overview[M]. USA:Xilinx, 2012.

[2]Xilinx. Virtex-6 FPGA GTX Transceivers User Guide[M]. USA:Xilinx,2011.

[3]李大鵬,陳長勝,王世奎等.基于FPGA的高速串行傳輸接口研究與實現[J]. 航空計算技術,2008,38(2):100-103.

[4] Abhijit Athavale,Carl Christensen.High-Speed Serial I/O Made Simple[J].USA:Xilinx

Corporation.2005.4.

[5]徐文波,田耘.Xilinx FPGA 開發使用教程[M].北京:清華大學出版社,2012.7. [4] Xilinx.Virtex-5 FPGA [6]RocketIO GTX Transciver Wizard v1.5 Getting Started Guid[S].USA:Xilinx,2008

本文來源于中國科技期刊《電子產品世界》2016年第8期第42頁,歡迎您寫論文時引用,并注明出處。

評論