短波發射機自動功率控制異常波形采集系統設計

摘要:短波發射機自動功率控制中,算法設計缺陷或反饋控制系統故障可能導致輸出波形失真,甚至產生毛刺,損壞發射機功放或降低功放輸出效率。針對短波發射機自動功率控制波形檢測采集分析中的數據交互量大、實時性要求高等特點,提出了一種自動功率控制異常時波形實時采集設計方案。實驗表明,本設計不僅靈活可靠,且能滿足大量數據的實時交換要求。

本文引用地址:http://www.j9360.com/article/201608/296186.htm引言

音頻信號進入發射機經過調制后,通過信道功率控制使調制信號輸出電壓值逼近功放理想輸入值,從而提高功放效率。信道功率控制主要包括自動增益控制(AGC)與自動電平控制(ALC)。

實際工作中,調制信號經過信道功率控制后會有各種不同的瞬態響應,可能產生毛刺或發生包絡失真,從而降低通信質量,增大誤碼率,嚴重的可能損壞功放[1]。分析射頻信號的毛刺等高頻信號的變化特性、功率上升時間、包絡長期穩定性等參數,發現射頻信號采集分析系統可以檢測通信設備功率控制中是否存在設計缺陷或發生故障。這對于保證通信質量和保護功放,具有重要意義。

由于毛刺等高頻信號的變化特性往往是瞬態的,因此,對采樣檢測系統的采樣率和處理速度提出了較高要求。此外,由于信號包絡變化慢,延續時間長,因此,包絡失真檢測系統的存儲容量足夠大。

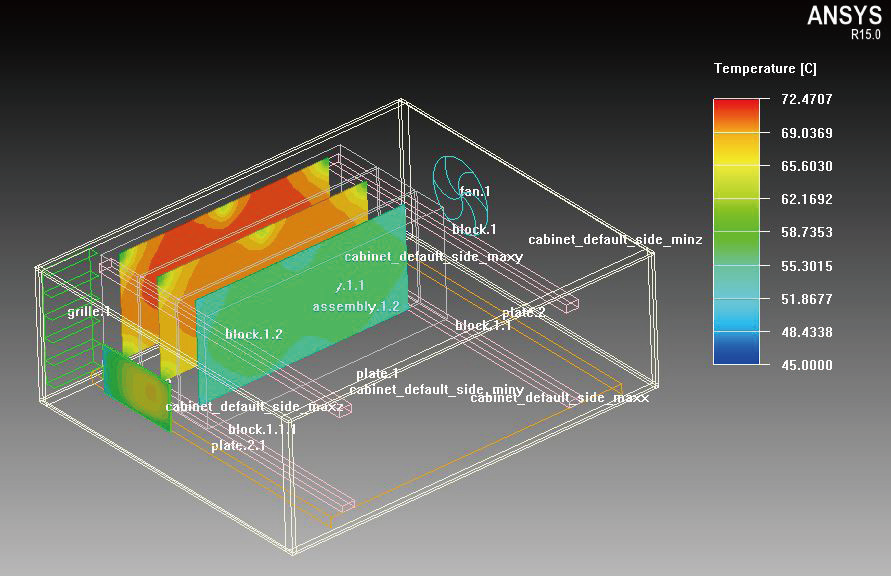

為實現整個系統功能,需要FPGA和DSP作為下位機,以完成毛刺檢測這類“高頻”信號特征檢測,并可將發現的異常波形標記后返回上位機。另外,由PC完成大存儲量、低速的“低頻”信號特征(包絡失真等)檢測。上位機與下位機之間的數據交互量大,實時性要求高,因此,需要一種數據傳輸更為可靠、傳輸速率更快的上位機與下位機之間的通信方案。

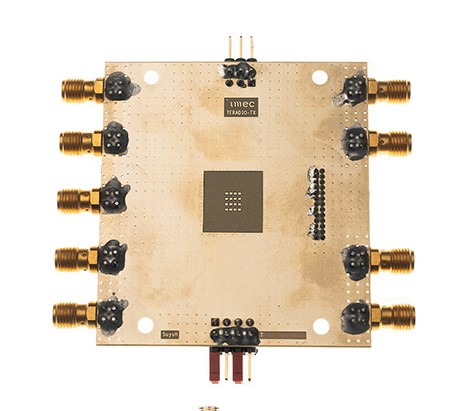

本文設計了一款可實現上位機與下位機大量數據實時傳輸的通信系統。下位機由DSP與FPGA構成,完成數字信號的初步處理,其中DSP完成復雜算法及控制任務,FPGA完成實時性要求高、運算量大的毛刺識別等高速信號處理。上位機程序則利用MATLAB編程,完成實時性要求不高但數據量較大的信號處理及顯示控制任務。上位機與ARM之間通過以太網連接,基于UDP協議實現。ARM通過HPI接口控制DSP,實現數據采集和命令控制。

1 總體設計

1.1 系統結構

PC機的各類并行總線通常無法直接連接機外高速并口設備,如各類DSP的高速主機接口(HPI,Host Port Interface)。本文采用ARM作為DSP與PC之間的橋梁。PC與ARM之間采用以太網通信方式,ARM與DSP在同一電路板上集成,從而解決了并行高速總線的連接問題,使系統設計簡潔,應用方便,同時滿足高速數據傳輸的要求。

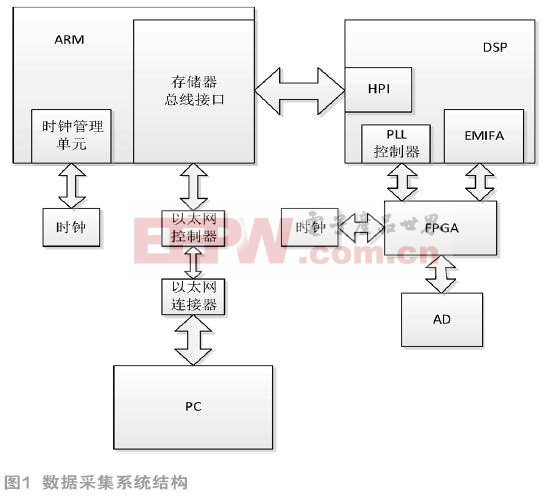

圖1顯示了系統的硬件結構框圖。從圖1中可以看出,上位機通過網線連接ARM,ARM控制DSP的主機接口,AD采樣的大量數據經過FPGA做相應處理后返回給DSP的EMIF接口。數據采集系統中,FPGA與ARM由各自晶振提供時鐘,FPGA對晶振頻率做鎖相處理后給DSP和A/D提供時鐘。

系統中,ARM控制板基于TI公司的LM3S9B96芯片;FPGA采用ALTERA公司StratixⅡ系列的EP2SGX30D;DSP選用了TI公司的TMS320C6416。

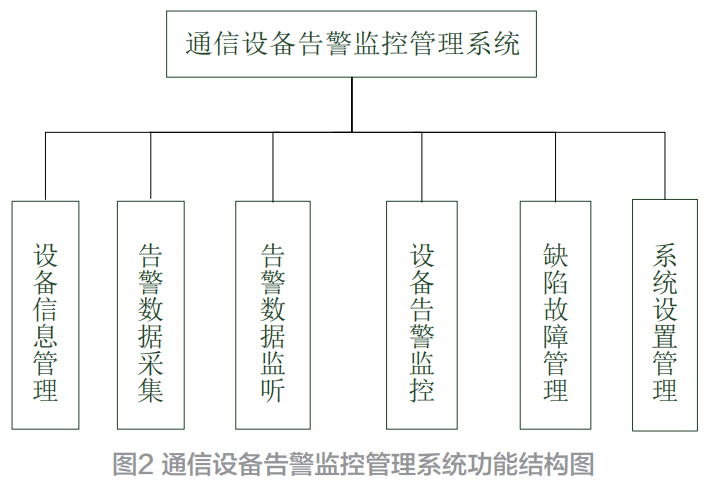

1.2 工作流程

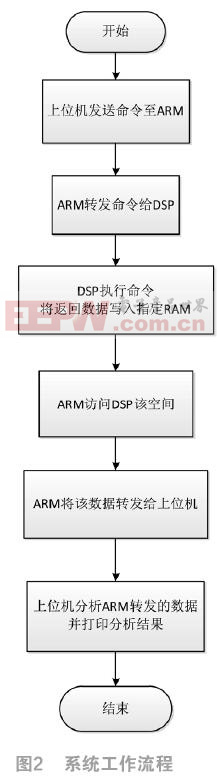

上位機與DSP完成一次通信的工作流程如圖2所示。從上位機發出的命令被處理成UDP報文形式后,經過以太網連接器與控制器進入ARM,再經過UDP協議解析后被轉發送至DSP。由于ARM直接控制HPI接口,因此,命令轉發過程即是ARM改寫DSP的RAM空間的過程。DSP收到命令后將解析報文,執行命令。執行完命令后,DSP將要返回給上位機的數據寫到之前定義好的RAM空間內。ARM之后將訪問DSP的RAM空間,即進行讀操作,將該數據整理成UDP報文形式,并通過網口轉發給上位機。DSP與ARM之間采用中斷方式通知對方新數據或命令的到來。

2 硬件設計

2.1 ARM控制板設計

ARM開發板硬件設計如圖3所示。本設計中的ARM開發板是基于TI公司的LM3S9B96芯片,其硬件模塊主要包括1個看門狗復位電路、1個網絡變壓器以及2個晶體振蕩器。

LM3S9B96的時鐘來源是主振蕩器(MOSC)或16MHz內部振蕩器(IOSC)。最終產生的系統時鐘用于Cortex-M3處理器內核以及大多數片內外設。本設計中,主振蕩器通過外部單端時鐘源連接到OSC0輸入引腳,以提供頻率精準的時鐘源。

看門狗復位電路是一個定時器電路。正常工作的MCU每隔一段時間輸出一個復位信號到看門狗復位電路輸入端,給WDT清零。若超過規定時間未發送復位信號(一般在程序陷入死循環時),WDT定時超過后,看門狗電路就會發出一個復位信號到MCU,使MCU復位,防止MCU死機[2]。

LM3S9B96芯片集成了MAC和PHY功能,只需要連接集成變壓器的RJ45網口和必要的阻容器件,便可以實現以太網通信。

2.2 DSP主機接口(HPI)設計

上位機通過ARM可訪問主機接口(HPI)。主機接口是主設備或主處理器與DSP的通信接口。在C6x系列DSP中,主機接口是一個16位或者32位寬的并行端口,可以實現并行高速數據傳輸[3]。上位機掌管該接口的控制權。通過上位機不僅可以直接訪問DSP所有的存儲空間,而且可以直接訪問DSP片內存儲空間映射的外圍設備。

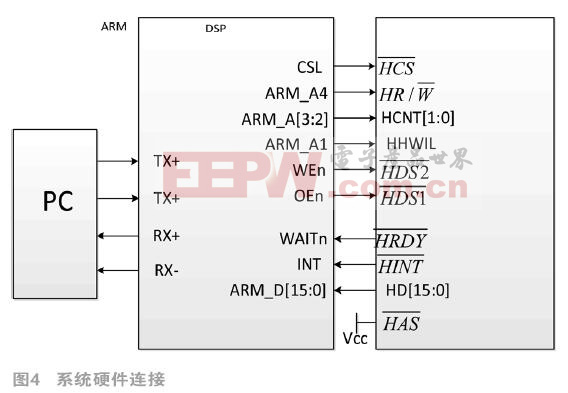

系統硬件連接如圖4所示。本設計中,ARM的地址線AMR_A[4:1]復用為HPI接口的控制信號。HCNTL[1:0]用作接口功能選擇,用來區分外部主機當前訪問的HPI寄存器種類[4]。

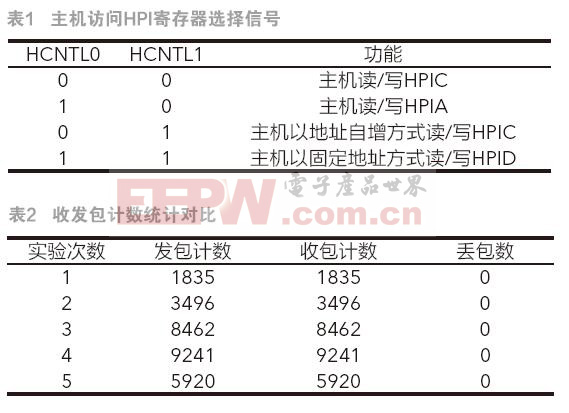

表1描述了主機訪問HPI寄存器的選擇信號HCNTL[1:0]。HR/W信號決定當前對HPI接口是讀或寫的操作。內部HPI選通信號來源于3個輸入信號HCS、HDS1和HDS2。HCS輸入用于使能HPI、HDS1和HDS2信號控制著HPI的數據傳輸。通過這些信號控制線可以順利實現HPI的讀/寫操作。

上位機通過網口與ARM開發板連接,信號均為差分輸入,差分輸出。

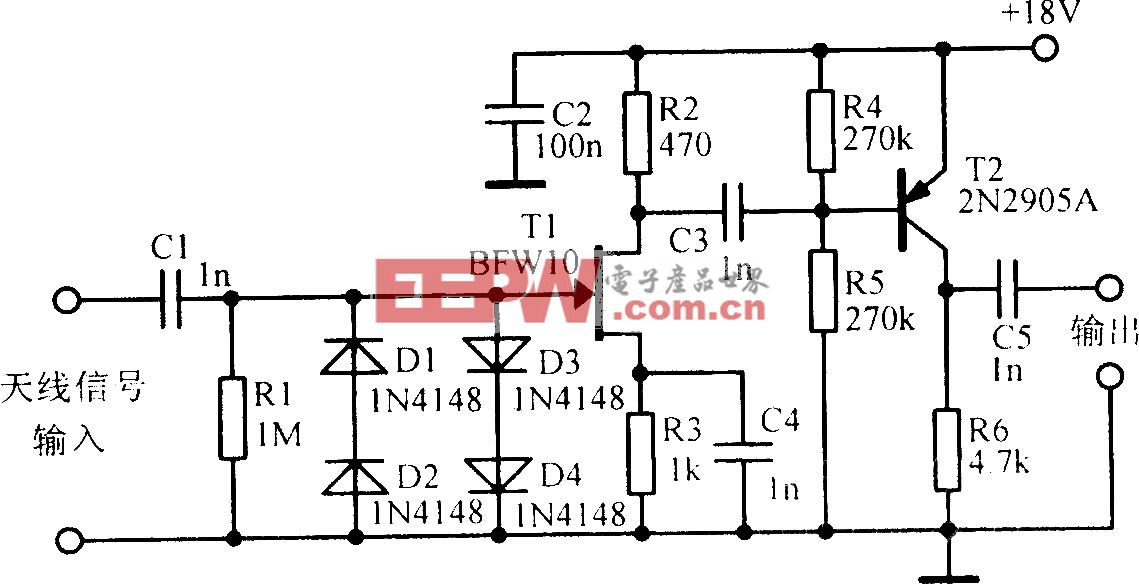

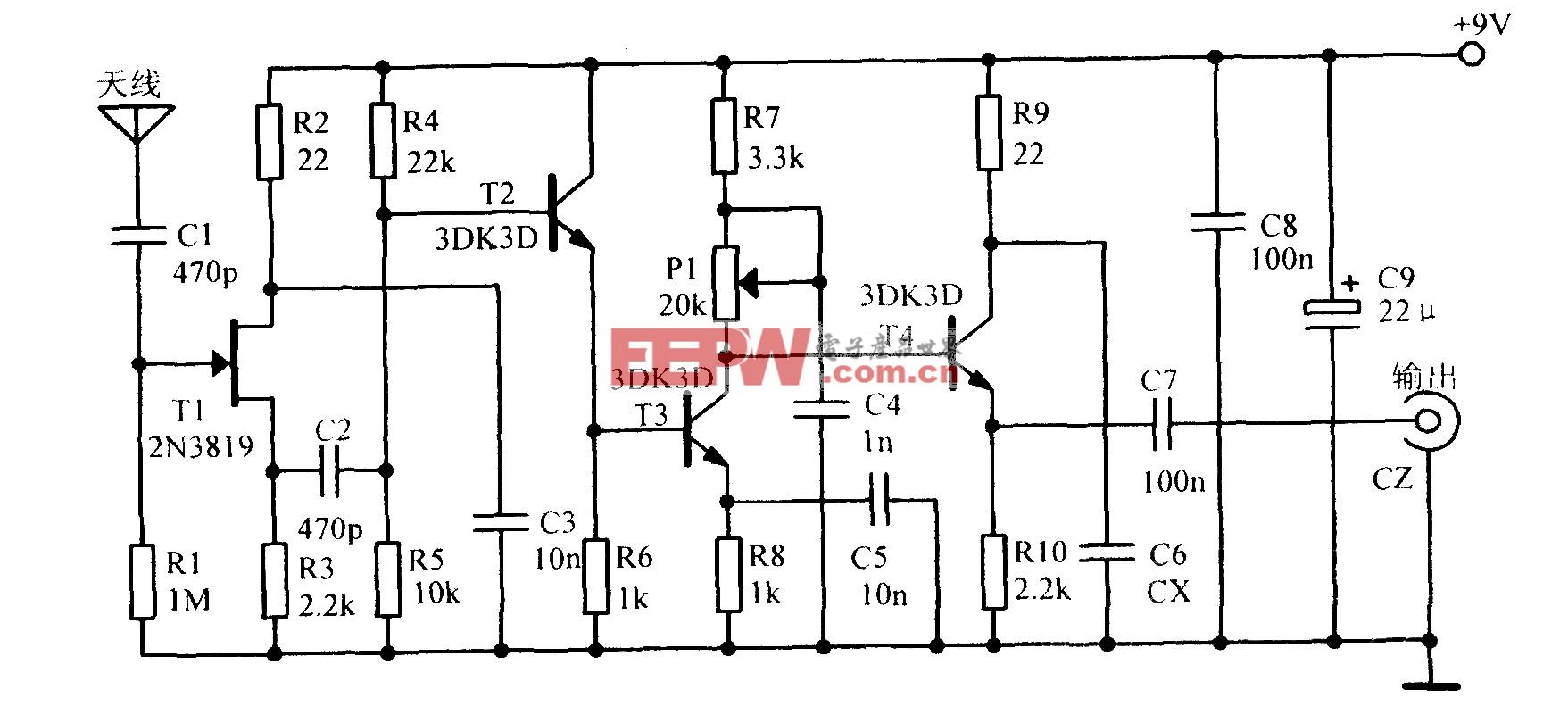

2.3 射頻信號采集

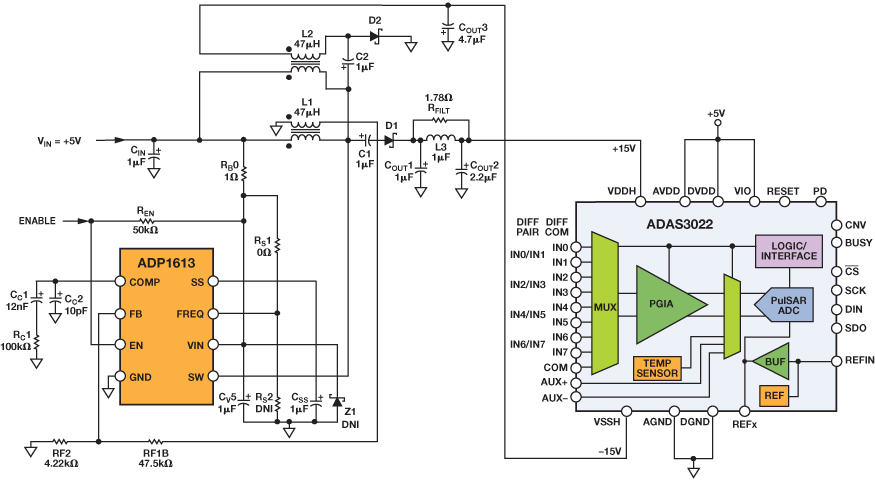

射頻信號采集采用ADI公司的AD9637實現。AD9637可同步將8路模擬射頻信號轉換為數字信號,轉換精度有10bit與12bit可選,轉換速率最高可達80MSPS,最大數據量為480MSPS,用戶可通過芯片的SPI控制口對AD9637進行設置。

本設計中,DSP通過FPGA實現SPI接口與AD9637通信。考慮到實際采樣信號為2M~30M的短波射頻信號,設置AD采樣時鐘為62.5MHz,并使用斬波(CHOP)模式,從而使其具有較小的低頻分量。

3 軟件設計

3.1 基于MATLAB的上位機軟件設計

上位機程序基于MATLAB R2012a開發。利用MATLAB圖形用戶接口開發環境(GUIDE)可以方便地建立GUI對象,同時建立M文件框架。用戶在該框架下編寫GUI組件的回調函數,可以控制并決定GUI對用戶操作的響應。

本設計中,DSP負責實時高速采樣的分析。DSP將采樣數據發送至上位機,MATLAB負責大量非實時低速信號的分析。上位機與ARM之間的通信基于UDP協議,即用戶數據報協議。UDP協議提供面向事務的簡單不可靠信息傳送服務,屬于傳輸層協議。雖然UDP不提供數據包分組、組裝,不能對數據包進行排序,在網絡環境較差的情況下存在丟包問題,但其有簡單、高效的優點。在本設計中,PC與ARM通過網線連接,傳輸距離不遠,網絡質量較好,不必考慮丟包問題。

UDP報文一般分為首部和數據區兩部分。本設計中,首部內容包括源端口、目的端口、報文長度與校驗和[5]。MATLAB軟件提供了UDP對象的創建函數。本設計在此基礎上設計了頂層協議,并根據協議編寫了數據讀取程序,將讀取到的數據打印或存入工作空間,進行包絡失真等檢測[6]。

在上位機給DSP下達命令前,需要對發送端與接收端的參數進行設置。參數設置包括本地IP地址、本地發送端與接收端端口號、遠端IP地址、遠端數據發送端和接收端的端口號。基本參數設置完畢后,將設置接收端緩存大小。然后,打開接收數據端UDP,在后臺等待下位機數據。

上位機發送命令時,預先設置發送數據端緩存大小;打開發送數據端UDP后,發送命令;數據發送完成后,關閉發送數據端UDP。

3.2 下位機軟件設計

3.2.1 ARM控制板軟件設計

本設計中,ARM主要負責上位機與DSP之間的通信,以Keil uVision4作為開發環境,C++語言為開發語言。

在實現上位機與DSP通信前,ARM先進行初始化。初始化過程包括設置系統時鐘、EPI總線初始化、設置本地IP、目標IP及物理地址等參數,設置回調函數響應中斷、定時器初始化以及清中斷。設計中定義的回調函數包括ARM向DSP轉發命令函數與ARM向上位機轉發數據函數。定義完回調函數后,回調函數的函數指針會注冊給調用者。當收到來自上位機或DSP的中斷后,ARM將使用函數指針調用指定的回調函數對事件進行處理[7]。

初始化完成后,ARM的IP地址、HPI接口控制寄存器、地址寄存器的初始值均設置完畢,開始等待上位機發來的命令,即等待中斷的過程。DSP返回數據給ARM前,同樣也會給ARM硬中斷,從而通知ARM對DSP進行讀操作。當收到來自上位機或DSP的中斷后,ARM會根據特定中斷調用事先定義好的回調函數,實現命令或數據的透傳[8]。

3.2.2 DSP主機接口控制軟件設計

HPI接口通過EDMA控制器與內存空間相連,因此,上位機訪問DSP內存空間時不需要DSP的CPU參與。主機通過操作3種不同的HPI寄存器實現對DSP內存的訪問,分別為控制寄存器(HPIC)、地址寄存器(HPIA)和數據寄存器(HPID)[9]。

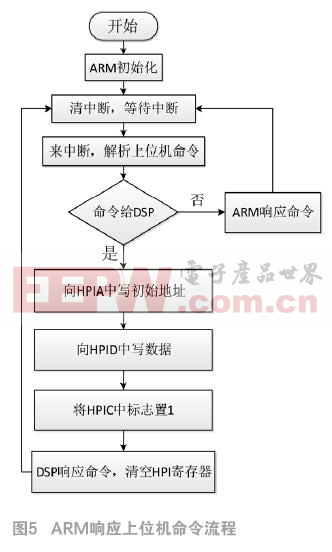

中斷后,ARM將執行之前定義好的回調函數,接收UDP報文并解析。上位機既可以通過網口給ARM發送命令,也可給DSP發送命令。ARM收到來自上位機的中斷后,會先將命令解析,分析是否是給自己的命令。若是,則將命令透傳給DSP。ARM透傳命令給DSP時,將訪問DSP的RAM地址,命令內容寫入相應寄存器,并改寫控制寄存器,通知DSP訪問該空間并執行命令。DSP執行完命令后,將數據寫入之前定義好的RAM內,拉低HINT,通知ARM訪問該空間并將數據轉發給上位機。ARM收到上位機命令后的工作流程如圖5所示。

4 實驗驗證

本文通過對下位機數據發送包計數與上位機數據接收包計數進行統計對比,得出此通信方案的可靠性。經過多次實驗對比,部分收發數據包計數統計如表2所示。可見,上位機收包計數與下位機發包計數結果基本一致,說明本通信設計方案可靠性高,且滿足大量數據實時交換的要求。

5 結語

本文設計并實現了一種以ARM為橋梁實現上位機與DSP通信的嵌入式系統,給出了系統設計總框圖,介紹了ARM與DSP通信接口設計、上位機程序設計以及系統開始工作后信號在系統中的處理及流程。本文設計的通信結構高速、穩定且易于調試,可推廣應用到各種信號采集和控制系統的設計中。

參考文獻:

[1]趙儉,張效義,于永莉.突發通信模式下數字自動增益控制的FPGA實現[J].艦船科學技術,2006,28(03):53-55.

[2]孫雪飛,胡巍.例說TI ARM Cortex-M3--基于LM3S9B96[M].北京:北京航空航天大學出版社,2013.

[3]汪安民,張松燦,常春藤.TMS320C6000 DSP實用技術與開發案例[M].北京:人民郵電出版社,2008.

[4]熊斌,趙曙光,郭星明.一種多路視頻處理系統新方案[J].通信技術,2011,44(05):116-118.

[5]蔡鈞,段文偉,付俊杰等.一種改進的DCS通信接口方案及應用[J].自動化儀表,2011,32(08):50-52.

[6]Chia-han Y,Gulnara Z,Yang Chen-Wei,et al.Cosimulation Environment for Event-Driven Distributed Controls of Smart Grid[J].IEEE Transactions on Industrial Informatics,2013,9(03):1423-1435.

[7]裴科,張剛.一種互補性多處理器系統中OS間通信接口設計[J].計算機工程與應用,2010,46(17):60-62.

[8]曹理發.基于ARM+DSP的視頻處理系統設計與實現[D].武漢:武漢理工大學,2008.

[9]吳劍劍.一種基于ARM+FPGA+DSP嵌入式實時圖像處理平臺設計與實施[D].武漢:華中科技大學,2012.

本文來源于中國科技期刊《電子產品世界》2016年第8期第38頁,歡迎您寫論文時引用,并注明出處。

評論