基于Microblaze軟核FSL總線的門光子計數器設計與實

摘要:門光子計數器是量子光學實驗中單光子探測常用的數據采集設備,用于收集單光子探測器探測到的單個光子信號。由于不同的場合需要用到不同的計數模式,商用的計數器往往難以滿足具體的需求,或者造成采集效率低下。系統采用的是一種基于MicroBlaze系統FSL總線的可擴展計數器設計架構,該架構能夠靈活的添加不同的計數功能,并通過統一的FSL總線和Microblaze CPU與PC通信。在該架構的基礎上實現了針對量子單自旋調控實驗中常用的計數模式。系統所采用的設計和實現方式可以推廣到其他光子計數需求中,并具有較低的設計和生產成本。

關鍵詞:計數器;Microblaze;FSL

0 引言

光學領域尤其是量子光學領域的實驗常常需要進行單個相干光子的探測用于實現實驗數據的采集。一般常用的配置是一個單光子探測器加上一個門光子計數器,其前端的單光子探測器用來收集光子信號,每探測到一個光子產生一個TTL脈沖,后端的門光子計數器用來記錄該TTL上升沿數目并且與PC等其他器件通信或者同步。APD的工作方式相對簡單,而門光子計數器則由于具體實驗需求不同而要求不同的工作方式,很難有一種通用的計數模式能夠滿足各種情況的需求。由于成本限制,功能固定的計數器往往因為沒有廣闊的市場而造成價格很高。另一方面,工業和科研界購買的商用計數器往往無法滿足自己的具體需求而導致工作效率低下,甚至無法滿足要求。

所謂門光子計數器就是針對單自旋量子調控實驗研究中對單個光子探測的需求所研制的。單自旋量子調控是對晶體中的缺陷,如量子點和金剛石色心進行控制,其信號讀出一般是通過自旋發生的單個光子進行探測實現的。在此類實驗中常用的技術有三種:門光子計數、定時計數和相關函數測量。文中所述的系統建立了一種可擴展的通信和控制架構能夠添加不同方式的計數功能。

1 系統結構設計

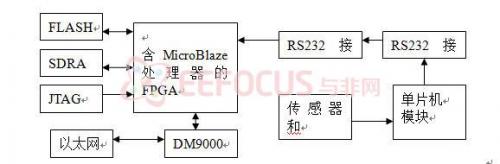

整體系統結構示意圖如圖1所示,通過PC機的以太網口實現與計數系統的數據通訊與命令傳輸,PC機將工作模式選擇等命令通過網口向系統發送,而系統將在不同模式下的計數值及計數狀態等數據通過網口發送到PC機,交由PC機對數據進行處理。系統的主芯片采用Xilinx的SPARTAN 3E系列的XC3S500E。系統的光子計數輸入由兩個BNC接口引入,這兩個接口可以由FPGA進行配置,使光子計數器以不同的模式進行工作。系統的固件燒寫在FLASH芯片內,SDRAM提供了大容量存儲空間,用于運行時裝載Microblaze軟核代碼、計數應用代碼以及存儲計數的數據。

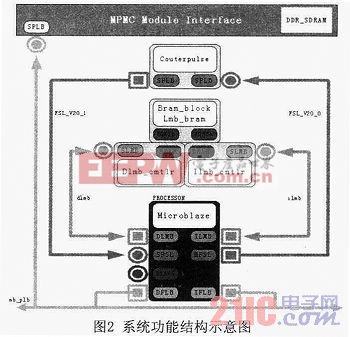

系統以FPGA為處理中心,實現各種工作模式,其功能框圖如圖2所示。功能模塊主要包括軟核Microblaze、對外部存儲器的接口MPMC、以及需要設計實現的Counterpulse IP核。在Counterpulse IP核與處理器軟核之間,采用了FSL總線進行連接,實現由Microbalze對Counterpu-lse核的配置,以及由Counterpulse核到Microblaze的數據傳輸。

系統工作時,由Microblaze軟核通過網口接收由PC機發送來的命令,根據命令,通過一路FSL總線對光子計數IP核進行工作模式的選擇和配置。計數IP核對外部計數源進行計數,計數的結果和狀態數據通過另一路FSL總線發送到Microblaze軟核,由Microblaze軟核將該數據在DDRRAM內進行緩沖,并通過網口將這些數據最終發送給PC機,由PC機進行分析處理。

系統有三種工作模式:模式一:使能計數,使能信號有效時(高電平有效),對光子計數輸入的計數脈沖信號進行計數;模式二:定周期計數,根據設定的計數周期,對光子計數輸入的計數脈沖信號進行計數;模式三:啟動和停止信號分開的計時,根據輸入的計數啟動信號和計數停止信號(均為上升沿有效),進行以系統基頻為基準的計時,以實現函數測量。

評論