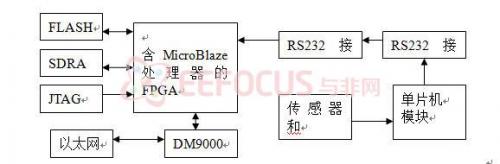

基于Microblaze軟核FSL總線的門光子計數器設計與實

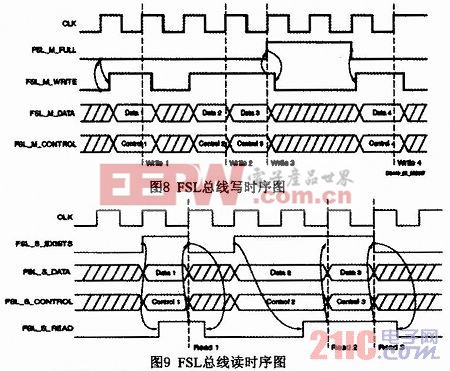

由于FSL總線是單向的,所以系統(tǒng)中采用了兩條FSL總線,實現Mieroblaze到計數IP核之間的雙向通訊,計數IP核在面對兩條FSL總線時,擔當的分別是MASTER(主)和SLAVE(從)兩種角色。因此,fsloprt.v的代碼應該同時滿足與FSL總線接口的讀和寫時序。讀寫時序如圖8和圖9所示。本文引用地址:http://www.j9360.com/article/194785.htm

3.4 計數IP核和FSL總線的在EDK中的連接實現

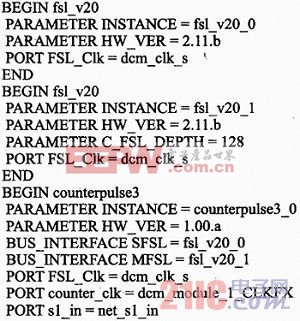

為了能使用FSL總線,首先應該在XPS圖形界面中對Microblaze進行配置,在Buses中將Number of FSL Links設置為1。再在IP Catalog中將FSL總線加入到工程中兩次。

在計數IP核編寫后并綜合通過后,將該IP核導入到XPS工程中。

在XPS中,分別對Microblaze和計數IP核的MFSL和SFSL進行連接,將Microblaze的MFSL端連接到計數IP核的SFSL端,反之將計數IP核的MFSL端連接到Microblaze的SFSL端。并在system.mhs中進行如下配置:

![]()

由于從計數IP到Microblaze方向數據量較大,所以對FSL總線的深度進行了配置,如上述代碼中,PARAMETERC_FSL_DEPTH=128,被配置為128級深度。

4 結論

在系統(tǒng)的設計中,光子計數IP核與Mieroblaze軟核之間通過FSL總線進行通訊,并且對FSL總線上的FIFO緩沖進行了深度擴充,大大增強了光計數數據的傳輸可靠性。由于系統(tǒng)將門光子計數的三種模式,以IP核的方式實現,相對于市場上商用的計數器來說,實現方式靈活,易于配置和擴展,這種方式為門光子其他可能潛在的計數需求留下了擴展的基礎,并具有較低的設計和生產成本。

評論