基于FPGA軟核的參數可變的壓力測試系統設計

爆炸沖擊波壓力測試是對常規武器系統殺傷力評價的有效技術手段,可為武器的威力對比,性能評估提供重要的依據。為了獲取整體信息,往往需要在測試現場布設數目較多的測試裝置。由沖擊波超壓經驗公式分析,超壓峰值隨著彈藥的當量和測點距爆心的距離產生十分顯著的變化。在實際測試中,要求測試系統根據實驗對象和測試環境合理設置參數。傳統的測試系統設計中,為了完成不同的測試任務,往往需要重新設計PCB電路。而設計新的系統不僅花費較大工作量和成本,并且開發周期長。另外,倘若測試系統需要完善和升級時,則難度較大。

本文引用地址:http://www.j9360.com/article/201610/308689.htm本文根據不同環境下的沖擊波壓力測試需求,設計了可配置的FPGA軟核,在硬件電路的基礎上,通過移植可配置的軟核,在較短的開發周期內,設計出測試參數可變的測試系統。解決了傳統測試系統的開發周期長、成本高、電路可復用性差等問題。對測試系統進行了實驗驗證后,應用到靜爆測試中,有效獲得了壓力數據。結果表明,系統具有很高的可靠性。

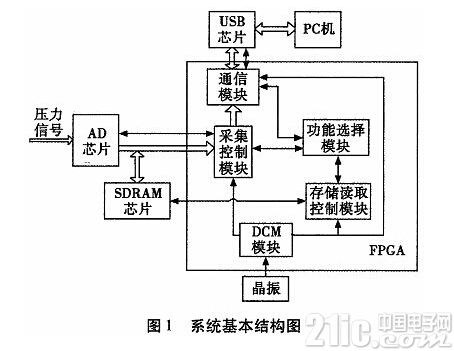

1 系統組成

由于測試環境惡劣并且爆炸存在極大的破壞性,極易造成測試系統的損壞。為了提高了系統的存活率和智能化,采用存儲測試技術,將傳感器及其調理電路、采集存儲電路、電源等集成一體,構成一個可獨立工作的微小系統。將其植入爆炸現場,完成沖擊波信號采集與存儲,實驗完成后回收測試系統,由計算機回讀數據并再現測試信息。測試系統總體組成如圖1所示,硬件由ICP壓力傳感器、調理電路(程控放大器、運算放大器、低通濾波器)、AD轉換器、FPGA、SDRAM存儲器及USB芯片等組成。軟件設計主要包括FPGA軟核和上位機。上位機采用LabVIEW設計,具有良好的人機交互界面,實現測試參數設置與回讀,數據讀取與顯示的功能。

本文研究重點是設計出滿足不同測試環境下的壓力測試系統可移植、可復用的軟核。通過調用所需要的功能控制軟核,配合周圍電路,完成沖擊波壓力測試。

2 軟核設計

FPGA具有可靜態重復編程和可動態系統重構的優點,因此可通過編程來達到修改硬件功能的目的。軟核設計是通過反復驗證的、具有特殊功能的宏模塊,可使這些編程數據進行移植和修改。只要對FPGA內部的邏輯模塊和I/O模塊進行配置后,即可實現相應的電路功能。同一FPGA輸入配置好的軟核,便可完成壓力測試的邏輯功能。軟核設計包括有:數據采集模塊軟核、參數設置模塊軟核、數據存儲模塊軟核、USB通信模塊軟核。

2.1 數據采集模塊軟核

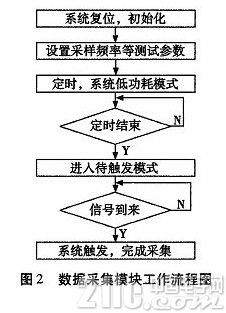

時鐘是同步電路系統設計的關鍵,系統采用了數字時鐘管理單元(DCM)管理和控制時鐘信號,以提供優質的時鐘信號源。由于每次實驗準備的時間不同,而觸發具有隨機性,有可能在準備期間因現場干擾造成系統誤觸發,導致測試失敗。為了提高系統可靠性和降低系統功耗,設計了定時和參數可變的功能。測試系統在現場布置好后,根據離彈藥爆破時刻設置定時長度。在定時時間內系統處于低功耗模式并且只有內部計數器在工作,其他模塊不工作。當定時結束后,喚醒系統,加載事先設置好的測試參數,進入待觸發模式,等待沖擊波信號的到來,完成數據的采集與存儲。數據采集模塊工作流程圖如圖2所示。

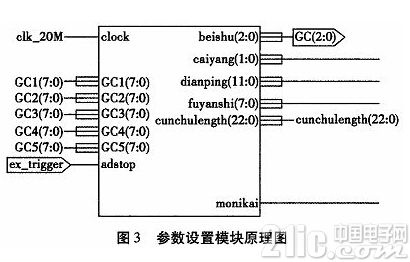

2.2 參數設置軟核設計

沖擊波超壓隨彈藥當量和距爆心的距離變化而變化,實驗前需根據布點的位置及測試對象,合理設置測試參數。主要包括:定時時長,觸發電平、放大倍數、采樣頻率、存儲長度、負延時。參數設置模塊原理圖如圖3所示,可通過上位機利用USB接口設置參數。

首先設定了一個合理的觸發電平值,當AD芯片采樣所得的電平值大于預設值時,則滿足觸發條件,否則不觸發。沖擊波信號一旦到來,此時給采集控制模塊一個信號以完成采集。然后根據測試環境預測測點的壓力大小,以選擇合理的放大倍數。模塊提供了1M,2M等不同采樣頻率,以完成不同測試任務。為了實現能觀測信號來之前的一段信息,設置了負延時,其大小決定了觸發前存儲的長度。另外,也可對數據存儲長度進行設置。以容納完整的信號為原則,對存儲長度、負延時進行合理的設置,以確保沖擊波壓力信號的完整性和連續性。

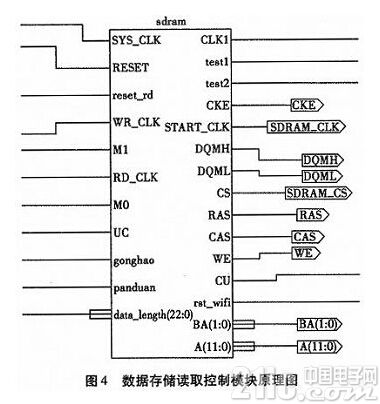

2.3 數據存儲軟核設計

爆炸沖擊波具有初值高、衰減快、持續時間短等特點,其測試是一個瞬態過程。為了有效地捕抓沖擊波壓力信號,選用PCB公司的ICP壓電壓力傳感器,其響應時間小于1 us,同時存儲器采用存取速度快的SDRAM。在AD采集完成后,不停地將數據循環存儲到SDRAM中,同時原數據將會不斷被新數據刷新覆蓋,當達到設定的存儲長度后會停止覆蓋,以存儲有用的數據。數據存儲模塊原理設計如圖4所示。

2.4 USB通信模塊軟核及其時序仿真

測試系統與上位機的通信是系統設計的關鍵環節。USB總線具有傳輸速度快、即插即用等優點。但復雜的USB傳輸協議和驅動,很大程度上限制了系統的設計與開發。為此,USB芯片選用FT245R,其內部集成了USB協議,完成并行數據與串行數據的雙向轉換。系統的參數設置和數據讀取是通過上位機完成的,上位機將相應的控制命令以串行數據存儲在FT245R的內部接收FIFO中;而FPGA的回讀信號和數據則以8位并行數據存儲在發送FIFO中。通過通信模塊軟核控制FT245R,實現數據的傳輸。

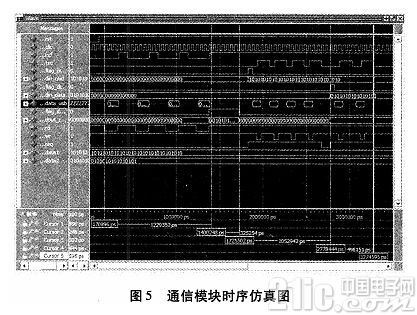

為了驗證通信軟核功能的正確性,利用Modelsim SE對其進行了時序仿真,如圖5所示。先進行讀操作,圖中高亮的data_usb的前4個bytes數據,表示上位機從FPGA中回讀的4個參數;然后進行寫操作,圖中data_usb的中間4個bytes數據表示上位機對FPGA設置的4個參數;而data_usb的最后2個bytes數據則表示上位機設置的2個命令。從時序圖可得,rxf和rd、txe和wr的時序,與FT245R芯片讀時序和寫時序完全相符,說明該模塊設計正確,功能滿足要求。

3 系統性能驗證

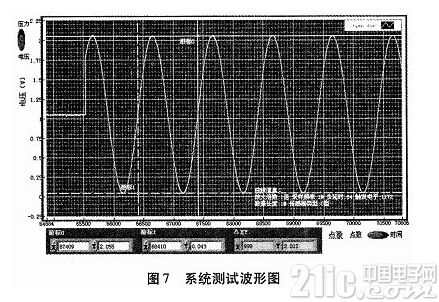

為了驗證采用軟核設計壓力測試系統的準確性和可靠性,進行了信號采集試驗。首先利用Agilenl公司的33521A信號發生器,產生頻率為1 kHz、幅值為2 V的正弦信號,如圖6所示。然后設置測試系統的參數,具體包括放大倍數:1倍,觸發電平:1172,采樣頻率:1 M,負延時:64 k,存儲長度:1 M。設置完成后,測試系統對正弦波信號進行采集。利用上位機通過USB接口讀取采集數據,并將數據及測試信息進行顯示,如圖7所示。

由圖可知:正弦信號實際頻率為1.000 0 kHz、幅值為2.018 V,而采集到的波形頻率為0.999kHz、幅值為2.012 V,測試誤差為0.297%,滿足設計要求,驗證了測試系統的準確性。另外,圖7右下方回讀的測試信息與之前設置的參數一致,進一步驗證了參數設置功能的正確性。

4 彈藥靜爆試驗

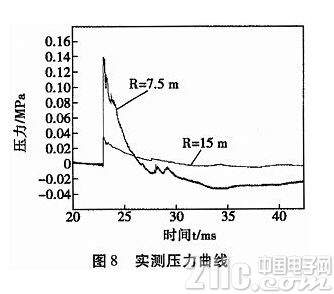

將20 kg的某裸裝彈藥架高1.5 m進行靜爆實驗,根據測試要求并盡可能保護測試系統,將設計好的2套測試系統分別埋設于在同一直線上距爆心7.5 m、15 m處。根據經驗公式,計算的沖擊波超壓峰值理論值分別為0.148 3 MPa,0.038 8 MPa。設置好合理的參數后,讓其均處于定時狀態,實驗人員安全撤離后按時進行爆破。實驗完成后,回讀數據。測試系統在7.5 m、15 m處測的沖擊波超壓峰值為0.139 2 MPa,0.034 3 MPa,接近理論值,實測壓力曲線如圖8所示。多次實驗表明測試系統可靠、穩定。

5 結論

針對不同環境下的沖擊波壓力測試,設計了可配置的FPGA軟核,實現對周圍硬件電路的控制,完成了瞬態沖擊波壓力信號的采集。根據不同測試條件,可對軟核進行重新配置,實現系統快速設計,提高了電路復用性。測試系統在多次實彈測試實驗中得到了應用,其穩定性、可靠性得到了驗證,并能有效獲取數據。

評論