- 引 言

隨著半導體制造工藝的發展,以FPGA(現場可編程門陣列)為代表的新一代可編程邏輯器件(PLD)的邏輯資源密度不斷增加,使得可編程技術很自然地就與系統芯片集成技術(SoC)的結合日益緊密,并逐步成為可配置平臺技術(configurable platform)的主流。

目前,各主要PLD廠商基于FPGA的可配置平臺雖然大都采用“微處理器十可編程邏輯”的架構,但在開發基于FPGA的嵌入式系統時,卻采用了各自不同的方式來整合處理器系統與片上的其他邏輯資源(大多數以用

- 關鍵字:

IP核 FSL MicoBlaze FPGA RISC OPB LMB

- 引 言

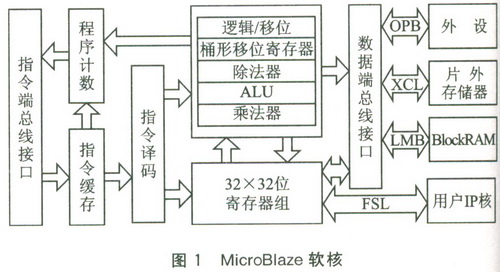

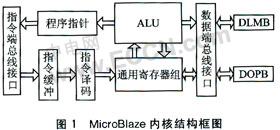

在基于MicroBlaze的SOPC系統中,將用戶IP核整合到基于MicroBlaze的嵌入式軟核處理器系統中,通常有兩種方法:一種是將IP核連接到OPB總線;另一種是將用戶IP連接到MicroBlaze專用的FSL總線上。盡管OPB和FSL總線都是MicroBlaze軟核與FPGA其他片上邏輯資源連接的主要途徑,但它們的分工足不同的。OPB總線適用于將要求低速和低性能的設備連接到MicroBlaze系統中;而FSL總線則適用于將對時間要求高的用戶自定義IP核,整合到基于MicroBla

- 關鍵字:

FSL UART IP核 SOPC OPB MicroBlaze

opb介紹

您好,目前還沒有人創建詞條opb!

歡迎您創建該詞條,闡述對opb的理解,并與今后在此搜索opb的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473