高速模數轉換器動態參數的測試

高速模數轉換器(ADC)的參數定義和描述如表1所示。

本文引用地址:http://www.j9360.com/article/194384.htm表1 動態參數定義

測試方案中的線路板布局和硬件需求

為合理測試高速ADC的動態參數,最好選用制造商預先裝配好的電路板,或是參考數據手冊中推薦的線路板布局布板,高速數據轉換器的布板需要高速電路的設計技巧,通常應遵守以下基本規則:

所有的旁路電容盡可能靠近器件安裝,最好和ADC在同一層面,采用表面貼裝元件使引線最短,減小寄生電感和電容。

模擬電源、數字電源、基準電源和輸入公共端采用兩個0.1MF的陶瓷電容和一個2.2M(F雙極性電容并聯對地旁路。

采用具有獨立的地平面和電源平面的多層電路板,保證信號的完整性。

采用獨立的接地平面時應考慮ADC模擬地和數字地的物理位置。兩個地平面之間的阻抗要盡可能低,二者間的交流和直流電壓差低于0.3V以避免器件的損壞和死鎖。模擬地與數字地應單點連接,可以用低阻值表貼電阻(1Ω~5Ω)、鐵氧體磁珠連接或直接短路,避免充滿噪聲的數字地電流對模擬地的干擾。

如果模擬地與數字地充分隔離時,也可以將所有的接地引腳置于同一平面。

高速數字信號線應遠離敏感的模擬信號線。

所有的信號線應盡可能短,而且無90(拐角。

時鐘輸入要作為模擬輸入信號來處理,遠離任何模擬輸入和數字信號。

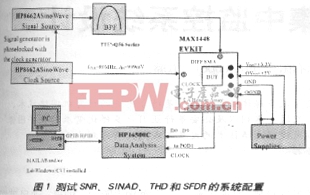

選擇恰當的測試方案和正確的測試設備是獲得數據轉換器最佳參數的重要環節。以下提出的硬件選擇方案對高速ADC MAX1448的測試是必需的,也是行之有效的。

直流電源 (Hewlett Packard E3620A, 雙電源 0-25V, 0-1A): 為模擬和數字電路提供獨立的供電電源。每個電源必須能夠提供100mA 的驅動電流.

時鐘信號函數發生器 (Hewlett-Packard HP8662A): 被測器件的時鐘輸入端接受兼容于CMOS電平的時鐘信號。由于MAX1448內部采用十級流水線結構、級間轉換依賴于外部時鐘上升沿和下降沿的可重復性,所以需用一個低抖動、快速上升/下降的外部時鐘信號。尤其是本轉換器的采樣出現在時鐘信號的下降沿,應確保下降沿的抖動最小。孔徑抖動限制了ADC的SNR性能:

SNRdB = 20·log10 (1 / 2π·fIN·TAj)

式中fIN 為模擬輸入頻率,tAJ 為孔徑抖動時間。欠采樣應用中對時鐘抖動指標要求更嚴格。

輸入信號函數發生器 (Hewlett-Packard HP8662A):

為保證正常工作,兩個函數發生器(時鐘與輸入信號)必須是相位鎖定的。

邏輯分析儀- (Hewlett-Packard HP16500C):

根據FFT所需的采樣點選擇邏輯分析儀,如HP1663C具有不到4k的數據記錄容量,可以用于本測試中。

模擬帶通濾波器(TTE 橢圓函數帶通濾波器 Q56 系列):

截止頻率:7.5MHz, 20MHz, 40MHz 和 50MHz

數字萬用表 (DMM): 用于檢查基準、電源和共模電壓。

被測器件的評估板

采用源自電路板的外部時鐘信號同步邏輯分析儀,并在時鐘的上升沿鎖相。采集數據時,數據可以存儲在數據采集板上、通過邏輯分析儀的HPIB總線進行數據交換,也可以存儲在邏輯分析儀的硬盤或軟盤中。

接著要考慮的是選擇合適的軟件工具。下列軟件工具被選擇用于數據的采集和分析:

* LabWindows/CVI:在邏輯分析儀和數據采集板之間建立通訊鏈路并進行數據采集。

* MATLAB:用于對所采集的數據進行FFT和動態參數分析的軟件工具,源程序可由Maxim中文網站獲得(www.maxim-ic.com.cn)。

用于測試的總體電路框圖如圖一所示。

評論