一種OTP存儲器片上時序信號產生電路的設計

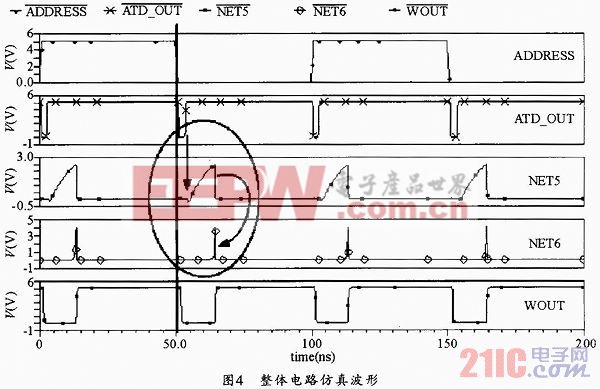

在TSMC 0.18μm工藝下,整體電路的仿真結果如圖4所示。當ATD_OUT的低電平到來時(圖2中垂直豎線標記處),就像前面2.2節分析的一樣,WOUT變為低電平;當ATD_OUT的低電平結束即上升沿到來時,NET5上的寄生電容被充電,圖4中可以看出NET5的電位逐漸抬升;當上升到反相器INV1的開關閾值VM時,從圖4中可以看出NET6發生從低到高的翻轉;從圖中可以看到NET6發生從低到高的翻轉使WOUT拉高;同時NET3也被拉高,迫使N6開啟將NET5清零,從圖4中可以看到NET5在被充電到VM后瞬間被拉低,NET6也瞬間變為0。從圖4的仿真結果可以很清楚的看出,WOUT的寬度主要由NET5充電時間T決定(還加上一個ATD_OUT自身的寬度)。控制T就可以控制WOUT的寬度。本文引用地址:http://www.j9360.com/article/193301.htm

3 結束語

文中設計的電路的主要功能是產生一個時序信號源。類似于自定時方法。例如,將該信號作為控制信號的信號源,可以通過簡單的延時、與、或等操作派生出相應的控制信號,這些信號就可用于控制存儲器內部各功能模塊如靈敏放大器以及鎖存器等。該電路的特點是時序信號源的寬度可控,通過調整電容或者充電電流可以得到不同的輸出脈沖的寬度,這可以結合存儲器中所需要的控制信號的寬度來決定。

評論