TD-LTE射頻一致性測試系統數字中頻單元設計

摘要:針對TD-LTE通信標準測試需求,設計一款可應用于“射頻一致性測試”的數字中頻處理單元。根據奈奎斯特帶通采樣原理直接對153.6MHz的TD-LTE/TD-SCDMA中頻信號進行模擬與數字的相互轉換,在FPGA中實現高效數字上/下變頻、移相濾波、多速率插值/抽取、成型濾波、符號同步、高速串行接口和離散傅里葉變換等功能,以正交I、Q信號輸出便于后續DSP對其進行軟件算法解調和處理。實驗結果表明,該方案能有效減少數字上/下變頻、插值/抽取資源消耗、增強接收通道的線性動態范圍、提高模數轉換器的有效分辨率、改善發射/接收通道矢量解調指標,適合作為TD-LTE射頻一致性測試系統數字中頻處理單元的實施方案。

本文引用地址:http://www.j9360.com/article/192732.htm引言

TD-LTE一致性測試包括“射頻一致性測試”、“協議一致性測試”和“無線資源管理(RRM)一致性測試”等,其中“TD-LTE射頻一致性測試儀器”在國內還是空白。

本設計來源于國家科技重大專項“TD-LTE射頻一致性測試系統”,其中“數字中頻處理單元”主要完成目標是:(1)實現TD-LTE(兼容TD-SCDMA)基帶信號數字上變頻、數字下變頻、多速率差值、多速率抽取;(2)采用高速數模轉換器實現高中頻信號輸出;(3)基于諧波采樣技術(欠采樣)利用高速模數轉換器實現高中頻信號采集;(4)采用多通道(2×2)MIMO空分復用技術,實現TD-LTE下行100Mbps上行50Mbps;(5)測試例功能:時域信號的RMS檢波自動功率控制、開/閉環功率測試(檢測)、發射關功率測試/發射開關模板,頻域信號的頻譜發射模板/占用帶寬/鄰道泄露抑制比,信號解調的矢量誤差幅度、星座圖等。

電路設計

數字中頻處理單元整體架構設計

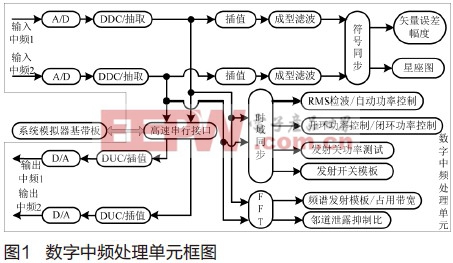

數字中頻處理單元硬件部分主要由FPGA[1-5]、DSP、模數轉換器(A/D)和數模轉換器(D/A)構成。數字中頻(IF)處理單元原理框圖如圖1所示。

上變頻與下變頻模塊設計

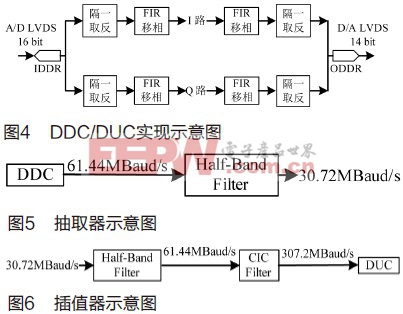

上變頻(DUC)與下變頻(DDC)模塊原理相近,采用相同設計方法,在FPGA具體實現上DUC是DDC逆向應用[6]。

該模塊設計根據奈奎斯特帶通采樣定理:

其中,Fs表示A/D或D/A采樣頻率,Fc表示載波頻率,B表示信號帶寬。

本設計A/D轉換器工作在諧波采樣(欠采樣)模式;D/A轉換器工作在基帶采樣(過采樣)模式,即中頻信號分別位于第三Nyquist區和第一Nyquist區。欠采樣與過采樣示意圖如圖2、3所示。

本設計DDC與DUC的Xilinx FPGA實現采用改進型方案,如圖4所示結構。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

模數轉換器相關文章:模數轉換器工作原理

數字濾波器相關文章:數字濾波器原理

評論