TD-LTE射頻一致性測試系統數字中頻單元設計

在FPGA中實現半帶濾波器與CIC濾波器,RAM資源消耗為零,且乘法器、查找表與寄存器消耗較少,具體資源分布情況如表2所示。

本文引用地址:http://www.j9360.com/article/192732.htm高速串行接口設計

LTE基帶信號數據吞吐量較大。本設計根據串行RapidIO協議在FPGA中,分別例化一個4X的SRIO(Serial-RapidIO)核用于基帶板和數字中頻板之間連接,同時例化1個1X的SRIO核用于數字中頻板內部FPGA與DSP連接。

測試例功能模塊設計

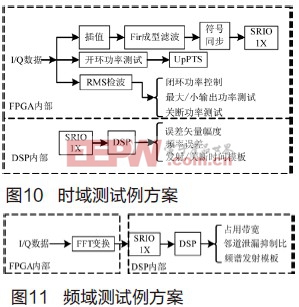

TS 36.521-1測量規范定義了LTE終端的發射機測試、接收機測試和性能測試的過程和測量方法。其中,終端發射機測試內容包括:(1)開環功率測量(OLP);(2)閉環功率控制(TPC步進量:1/2/3dB);(3)最大/小輸出功率測試(APC);(4)關斷功率測試(PVT);(5)發射/關斷時間模板(ECTM);(6)頻率誤差(FE);(7)誤差矢量幅度(EVM);(8)鄰道泄漏抑制比(ACLR);(9)占用帶寬(OBW);(10)頻譜發射模板(SEM)。

以上測試內容中,第1、2、3、4測試項由FPGA獨立完成;第5、6、7、8、9、10測試項FPGA作為預處理器,再由DSP處理后續復雜算法。

本設計測試例功能方案分時域、頻域處理兩部分,時域、頻域處理流程如圖10、11所示。

插值、成型濾波與符號同步子模塊設計

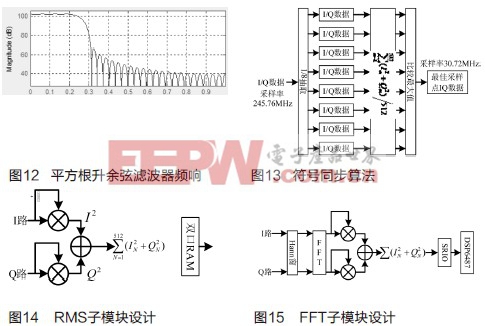

該模塊插值選用CIC插值器,差值倍數為8倍。成型濾波選取“平方根升余弦”FIR,符號同步采用“平均功率最大值”算法。平方根升余弦滾降因子選0.22,FIR階數為96階,頻響曲線如圖12所示。

FPGA中符號同步算法流程圖如圖13所示。

RMS子模塊設計

閉環功率控制測試、最大/小功率測試、關斷功率(PVT)測試和開環功率測試等模塊的檢波方式為“方均根”檢波(Root Mean Square),RMS定義如下:

xi表示某一時刻數據,N表示任一個連續取值的個數。由公式(15)可知,離散/數字信號的方均根(RMS)定義本身包含著“積分”概念,積分后的信號曲線有“平滑”的效果。該子模塊FPGA設計如圖14所示。

在FPGA中方均根檢波后,功率信號為I2+Q2,以此信號為基準,設計邏輯電路捕獲脈沖信號并保存至雙口RAM中,上位機主控軟件從RAM中獲取數據進行對數(logarithm)處理并顯示。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

模數轉換器相關文章:模數轉換器工作原理

數字濾波器相關文章:數字濾波器原理

評論