基于NiosII的二維條碼識別系統設計

摘要 隨著SOPC技術的日益成熟,基于SoPC技術的嵌入式系統得到廣泛應用。本文采用SOPC技術,以EP2C35為主控芯片,實現二維條碼識別系統的設計,并提出一種適用于嵌入式系統的PDF417條碼識別算法。實驗表明,該識別系統能夠快速準確地識別二維條碼,效果良好。

關鍵詞 SOPC 二維條碼 PDF417 嵌入式系統 NiosII

二維條碼PDF417中PDF為Portable Data File的縮寫,每一個PDF碼的儲存量可高達1 108字節,若將數字壓縮則可存放2 729字節。作為一種新的信息存儲和傳遞技術,PDF417具有成本低、信息可隨載體移動、不依賴于數據庫和計算機網絡、保密防偽性能強等優點,廣泛應用在國防、公共安全、交通運輸、醫療保健、工業、商業、金融、海關及政府管理等領域,PDF417碼的例子如圖1所示。

1 系統總體設計

本系統在FPGA上使用SOPC技術來實現無線手持二維條碼識讀器,與傳統一維條碼識讀器最大的區別在于完全脫離后臺數據庫,以及在高達50%破損率的情況下能夠進行高效率識別。

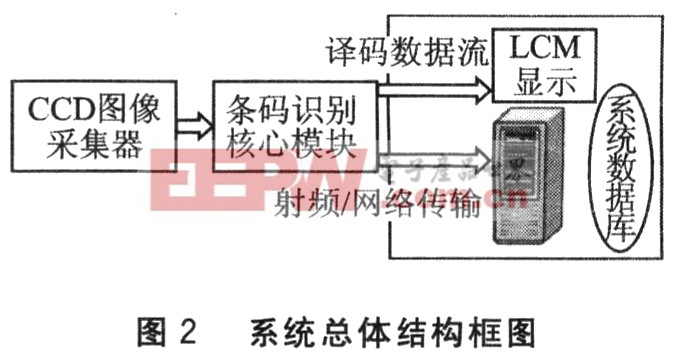

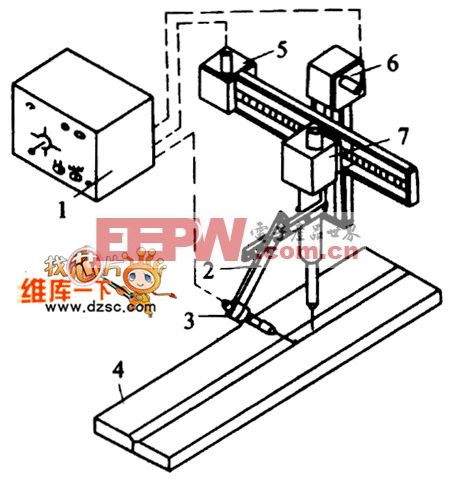

SOPC技術是一種基于FPGA解決方案的SOC,由美國Altera公司于2000年提出。基于SOPC平臺的開發結合了FPGA靈活可編程與片上。NioslI軟核處理器的用戶可配置等特點。在實現某功能時,通過在NiosII處理器下編寫C程序運行,也可以使用硬件模塊來加速。本系統綜合兩種實現思路,采用高性價比的Cyclone II EP2C35系列FPGA實現,系統總體結構如圖2所示。

整個系統由低到高分為三個層次:條碼識別的硬件平臺、μC/OS―II操作系統、條碼譯碼核心算法。最底層硬件平臺采用Altera公司的Cylone II EP2C35與ADI公司的視頻解碼芯片ADV7181B,具有8 MB的Flash存儲器,1.MB的SRAM等外設;中間層μC/OS―II操作系統提供任務調度和設備驅動,以及提供各種中斷來實現對外界請求的響應,如模式切換、LCM.顯示、射頻傳送等,有效地提高了系統運行速率;最頂層條碼譯碼核心算法包括了對條碼圖像的預處理和對譯碼數據的RS糾錯,采用C語言在NiosII的集成開發環境中(IDE)實現。

評論