FPGA開發中按鍵消抖與單脈沖發生器電路

FPGA開發中常用到單脈沖發生器。一些文章介紹過產生單脈沖的電路,產生的單脈沖脈寬和相位都不能與時鐘同步,只能用在要求不嚴格的場合。筆者目前從事的課題中需要一個與時鐘周期等寬,相位與時鐘周期相同的鍵控單脈沖發生器。鍵控單脈沖發生器需要按鍵產生單脈沖,但大多數帶有FPGA芯片的開發板提供的是高頻時鐘脈沖,按鍵時會存在抖動問題。為此筆者專門設計了按鍵消抖電路消除抖動,為產生單脈沖提供穩定的按鍵信號。

1 按鍵消抖電路原理

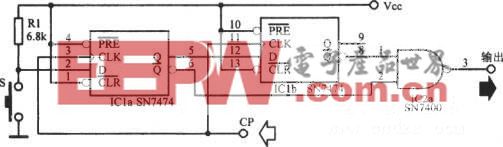

為了使按鍵消抖電路模塊簡潔,移植性好,在此用計數器的方式實現按鍵消抖的功能。

計數器模值n根據抖動信號的脈沖寬度和采樣脈沖信號CLK的周期大小決定。計數模值n=延時/脈沖信號采樣周期。一般按鍵抖動時間為5~10 ms,甚至更長。筆者用的開發板提供的系統時鐘為24 MHz,按公式計算,當計數器模值取20位,計數到219即h8 0000時,大約延時22 ms。計數期間認為是按鍵的抖動信號,不做采樣;計數器停止計數,認為采樣信號為穩定按鍵信號。這樣就可以把按鍵時間小于22 ms的抖動信號濾掉。

引入一個采樣脈沖信號CLK,并輸入按鍵信號KEY。KEY輸入低電平,計數器開始做加法計數,當計數到h8 0000即計數器中最高位Q19為1,計數器停止計數,輸出Q19,作為按鍵的穩定輸出,計數期間Q19輸出為0;KEY輸入高電平,計數器清零,Q19輸出為0。所以該電路需按鍵22 ms才會得到有效信號。

2 鍵控單脈沖發生器電路原理

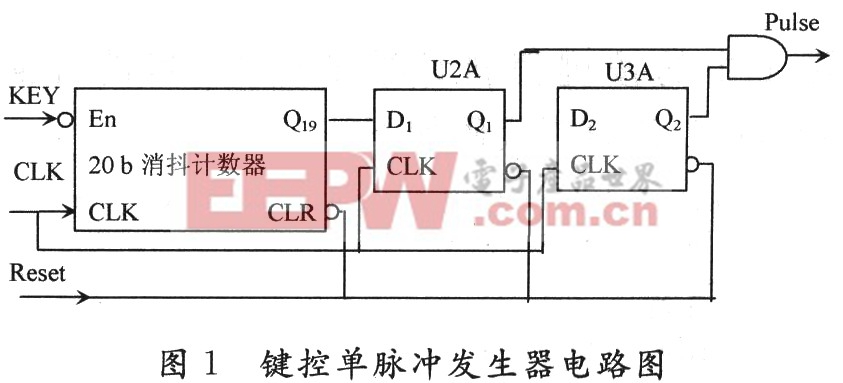

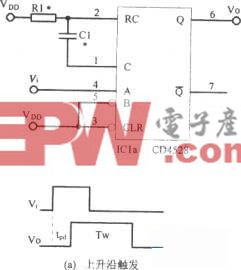

鍵控單脈沖發生器利用上述電路解決按鍵消抖問題,得到穩定的信號。用兩個D觸發器和一個與門產生單脈沖,如圖1所示。

D觸發器U2A收到穩定信號D1=1后被觸發。觸發器U2A中的Q1端得到與CLK同步的正向脈沖。輸出Q1到D觸發器U3A,得到比Q1延遲一個時鐘周期的的正向脈沖,將Q2端輸出取反得到一個負向脈沖。Q1與Qn2的輸出作為一個與門的輸入,會輸出一個脈寬是原時鐘周期2倍的單脈沖。

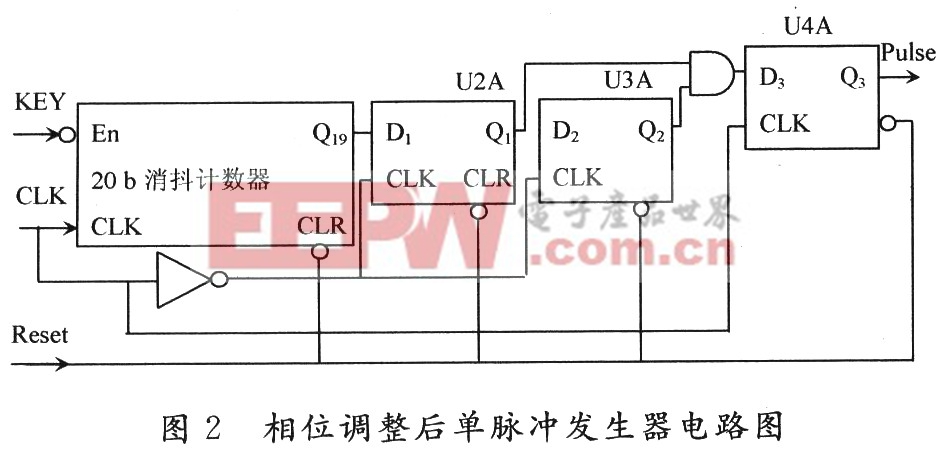

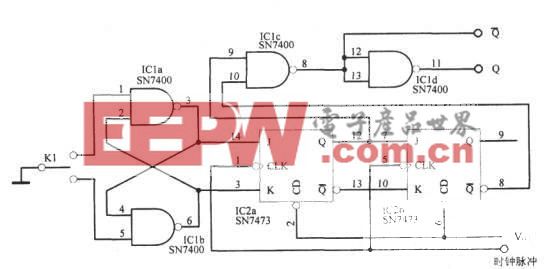

為了使得出的單脈沖脈寬與時鐘周期相等,相位與時鐘周期相同,對圖1中電路設計做了改進,如圖2所示。

評論