FPGA開發中按鍵消抖與單脈沖發生器電路

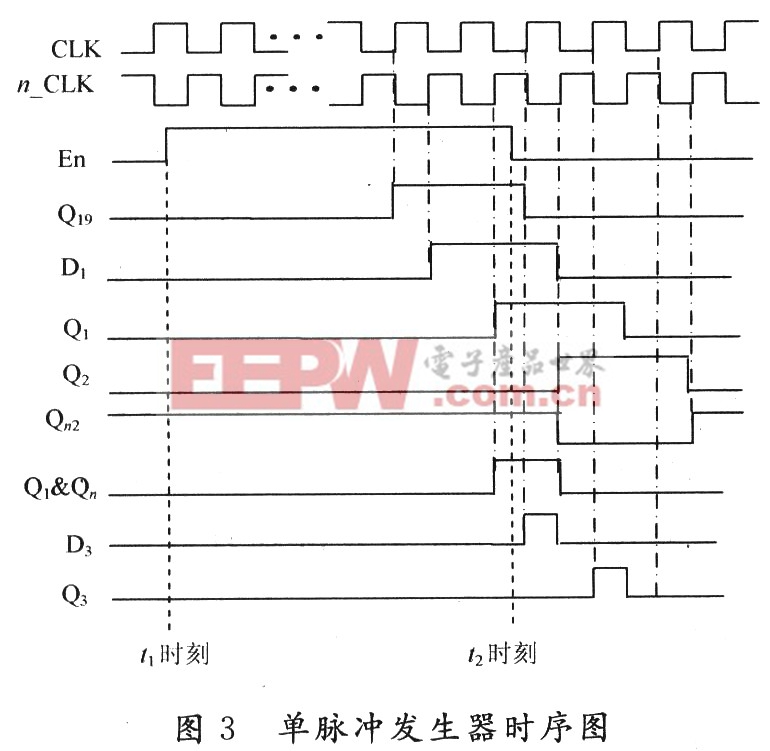

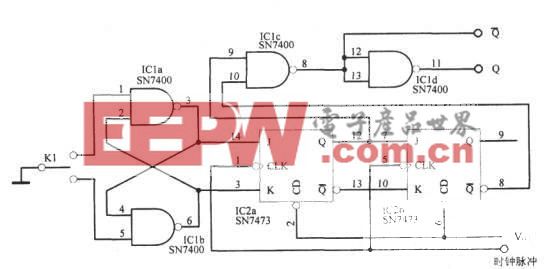

圖2中時鐘送入D觸發器前加了非門,使Q1端產生與nCLK(CLK的反向脈沖信號)同步的正向脈沖,與門輸出單脈沖與CLK差半個時鐘周期,作為D觸發器U4A的輸入D4,在CLK上升沿U4A被觸發,使單脈沖脈寬與時鐘周期相同,實現了等脈寬。并延遲了半個時鐘周期使輸出脈沖與時鐘周期對應,實現了相位調整。整個單脈沖發生器的時序圖如圖3所示(圖3中的t1,t2是任意鍵按下與鍵抬起時刻)。

3 基于FPGA下的按鍵消抖計數器和單脈沖發生器的Verilog HDL語言描述

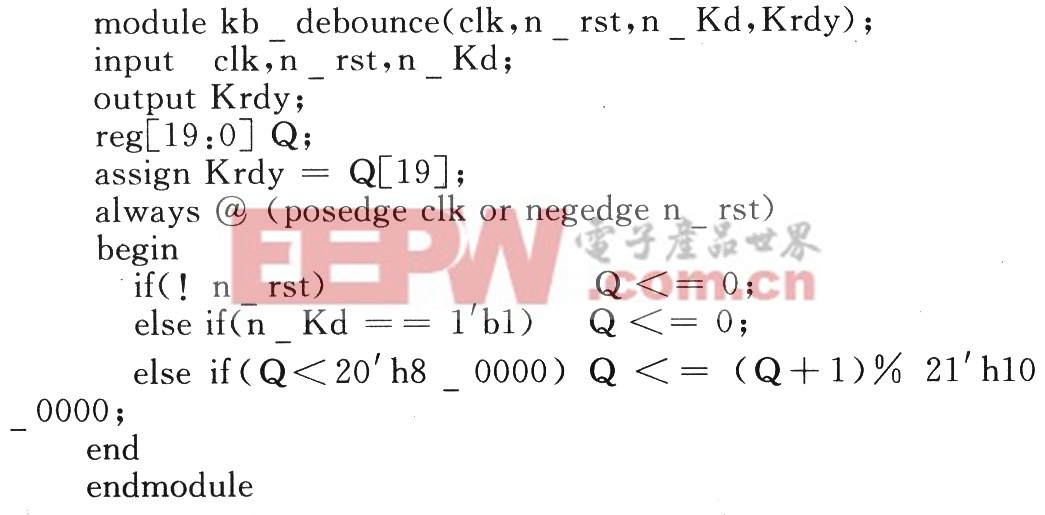

圖1中的按鍵消抖計數器電路,其進行描述的Verilog HDL語言代碼如下:

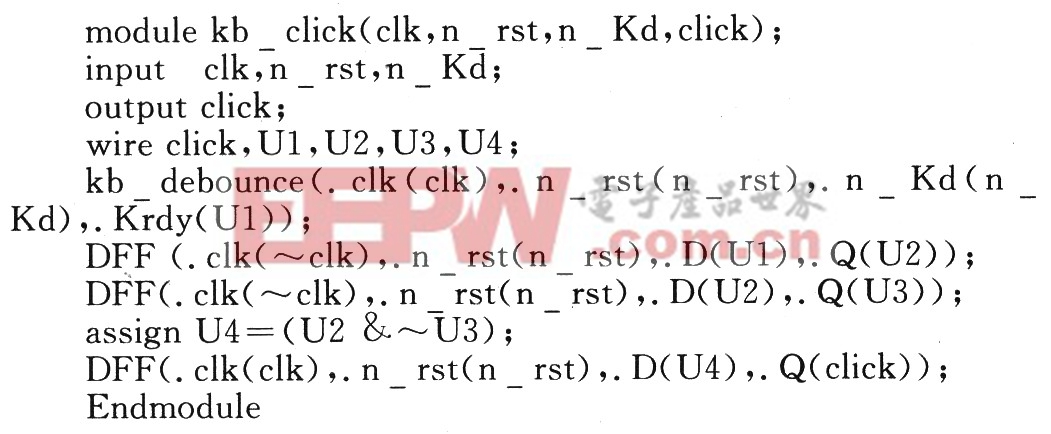

代碼中的復位n_rst和按鍵n_Kd都是低電平有效。鍵控單脈沖發生器的Verilog HDL語言代碼如下:

代碼中還用到了D觸發器DFF,實現這個模塊的代碼比較簡單,此處從略。

4 結 語

該文中的設計,實現了鍵控單脈沖發生器,產生脈寬等于時鐘脈沖,輸出脈沖與時鐘周期對應的單脈沖,并解決了按鍵消抖問題,可以應用到各種需要產生單脈沖的FPGA電路設計中。按鍵消抖電路可獨立地應用于其他FPGA電路設計中。本文中設計的20 b計數器是根據筆者課題需要而定。其他設計中可以根據按鍵抖動時間可利用公式計算出計數器模值設計計數器。

評論